Caravel template のシミュレーション

Caravel template の環境構築,サンプル回路の合成ののちにシミュレーションを行う手順を記載します. Caravel template では論理回路,論理合成後,遅延を含めた論理合成後の3つのシミュレーションが可能ですが,本ドキュメントでは,論理回路のシミュレーションのみを行います.

注釈

Caravel template 環境の回路合成はシャトルサービス向けのユーザ領域のみが対象ですが,シミュレーションではチップ全体と対象が異なります.

動作環境

本ドキュメントで対象としている mpw-9k では,論理合成後・遅延情報を含めた論理合成後のシミュレーションに不具合が発生する場合があります(mpw-9c など異なるリビジョンをお試し下さい).なお,論理合成後のシミュレーションでは大量のメモリや計算量を要します.

シミュレーション環境の設定

環境変数の設定を行い,シミュレーション環境の設定や波形表示ソフトウェア gtkwave を導入します.

cd Caravel_mpw-9k/caravel_mpw-9k

source ../setenv.sh

make simenv

sudo apt install -y gtkwave

Caravel template のシミュレーション範囲

Caravel の環境では,ユーザ回路だけでなく,Caravel 制御回路(RISC-Vプロセッサなど)や IO ポートを含んだチップ全体のシミュレーションが実行されるため,大きい計算時間を要します.また,複雑なシミュレーションでは制御回路の RISC-V のコードを記載することが必要となります.RISC-V のコードは,シミュレーションベクタで定義されている疑似 SPI-ROM に hex データとして格納します.(本ドキュメントでは RISC-V のコードはデフォルトのものを利用します)

Caravel template のシミュレーション呼び出し方法

Caravel template のサンプル回路では,外部 IO (GPIO),制御回路との Wishbone バス接続,内部ロジックアナライザの3つの入出力経路それぞれにシミュレーションが用意されています.

それぞれの入出力経路に対して,3つ(論理回路・回路合成後・タイミング)の方式でシミュレーションでき,計9種類のシミュレーションが行えます.

シミュレーション対象の入出力経路と方式の選択は,make コマンドのオプションで verify-(シミュレーション対象)-(方式) として指定することができます.

外部 IO の 論理回路シミュレーション

本ドキュメントは,外部 IO の論理回路シミュレーションを実行し,ユーザ回路(カウンタ)の値がユーザ用 IO へ反映されることを確認します.

make verify-io_ports-rtl

シミュレーションが実行され,下記のように外部 IO へカウンタ値が反映されている様子を確認することができます.

vvp io_ports.vvp

Reading io_ports.hex

io_ports.hex loaded into memory

Memory 5 bytes = 0x6f 0x00 0x00 0x0b 0x13

FST info: dumpfile io_ports.vcd opened for output.

MPRJ-IO state = zzzz1zzz

MPRJ-IO state = zzzz1zz0

MPRJ-IO state = zzzz1z00

MPRJ-IO state = 01001111

MPRJ-IO state = 01010000

MPRJ-IO state = 01010001

MPRJ-IO state = 01010010

MPRJ-IO state = 01010011

...

MPRJ-IO state = 11111011

MPRJ-IO state = 11111100

MPRJ-IO state = 11111101

MPRJ-IO state = 11111110

MPRJ-IO state = 11111111

Monitor: Test 1 Mega-Project IO (RTL) Passed

io_ports_tb.v:182: $finish called at 360462500 (1ps)

mv io_ports.vcd RTL-io_ports.vcd

rm io_ports.vvp

動作波形は,verilog/dv/(シミュレーション対象)/ のディレクトリに (方式)-(シミュレーション対象).vcd のファイル名で保存されます.本例では verilog/dv/io_ports/RTL-io_ports.vcd となります.

シミュレーションの動作波形の表示

動作波形を gtkwave に表示させて確認します.

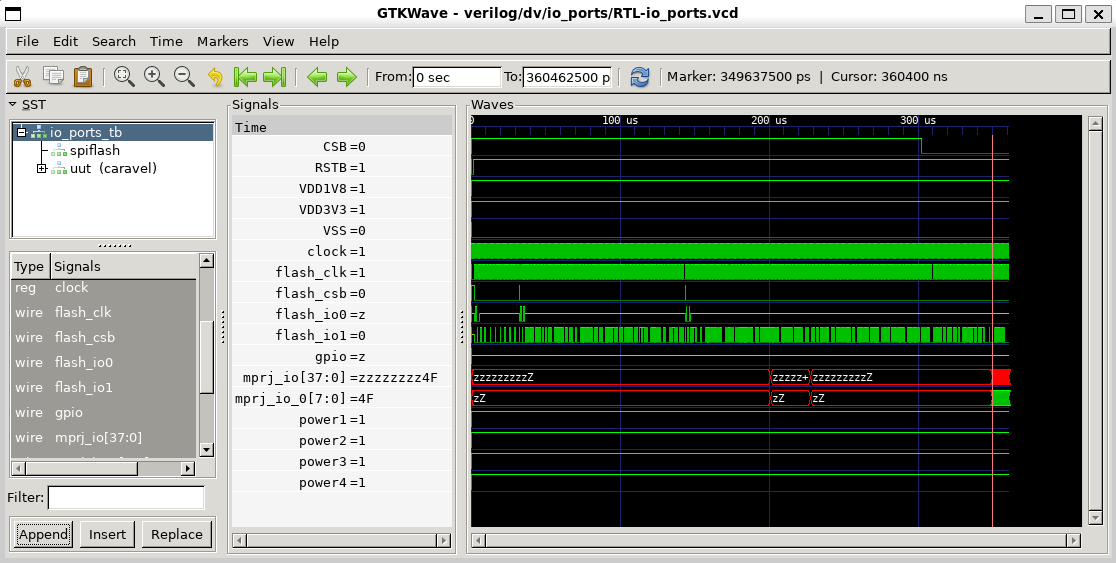

gtkwave verilog/dv/io_ports/RTL-io_ports.vcd

ウィンドウ中の SST から io_ports_tb を選択し,Type/Signals に表示される信号を選択して Append ボタンを押すことで,波形表示する信号を登録します.

Caravel のチップでは電源投入後の初期化後,制御用 RISC-V コアにて 外部 IO などの設定することでユーザ回路から利用できるようになります.上図では,およそ 360 us 後にカウンタの値が IO へ反映されることが確認できます.

制御用 RISC-V の命令列は外部の SPI-ROM に格納されており,1命令毎に数クロックのROMの読み出しが発生しています.(実チップでも同様に1命令の実行に数クロック要します)