# Low-Voltage Wide-Dynamic Range CMOS Log Domain Filter Using Companding Technique

January, 2008

DOCTOR OF ENGINEERING

Ippei Akita

Toyohashi University of Technology

©2008

Ippei Akita

All Rights Reserved.

#### Abstract

## Low-Voltage Wide-Dynamic Range CMOS Log Domain Filter Using Companding Technique

#### Ippei Akita

This dissertation proposes novel design techniques of low-voltage CMOS analog filters with wide dynamic range through the companding techniques. First, it is pointed out that an instantaneous companding integrator, which is a building block of continuous-time filters, has a degree of freedom to configure its topology, and then a synthesis method of all the integrators is proposed. Synthesized 45 integrators including known four ones are compared to each other by simulations, and some intrinsic features of each topology are found from the results. Two 1.0-V 2<sup>nd</sup>-order Butterworth low-pass filters fabricated in a 0.35- $\mu$ m CMOS technology as an application example of the integrators are also compared through its measured results. Furthermore, a selection of log domain integrator cores from the integrators is discussed for higher-order log domain filter design.

One of the selected log domain filter cores is used for syllabic companding filters the internal voltage swings of which are dynamically amplified as large as possible by sensing an input or an output signal of the filters. Combining log domain circuits with the syllabic companding technique, filters are easily implemented by use of one transistor as an amplifier, in which these filters are also called as dynamically adjustable biasing (DAB) ones because a gain of the amplifier is set by a dynamic bias current. Although a conventional DAB-based filter requires a supply voltage of 2.5 V, filters based on a modified DAB technique can operate at lower-supply voltages, 0.8 and 0.6 V, with keeping wide-dynamic range. Two 5<sup>th</sup>-order Chebychev low-pass filters are designed to confirm effectiveness of the proposed technique. The one is fabricated in a 0.35- $\mu$ m CMOS technology and the other is done in a 0.18- $\mu$ m one. The former achieves a 78-dB dynamic range at a power supply of 0.8 V. On the other hand the latter filter has a dynamic range of 89 dB and consumes 443  $\mu$ W, and then the filter is compared to other recently published filters through a figure of merit (FOM) which is calculated by use of dynamic range, bandwidth, filter order, and power consumption. The filter achieves an FOM of 3.83 fJ from a power supply of 0.6 V, which represents effectiveness of the proposed scheme in the view of a trade-off between a supply voltage and a dynamic range.

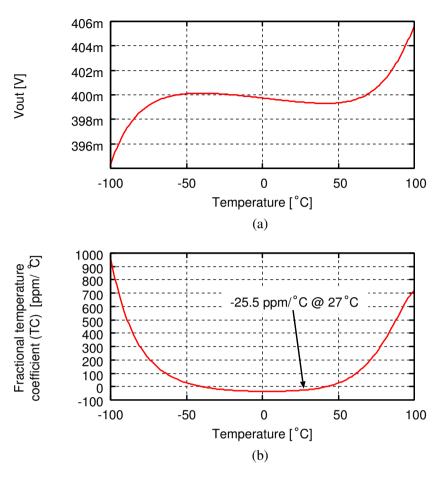

To design the filters with wider dynamic range in a short time, an optimum design method is presented. The method uses a signal-to-noise-plus-distortion ratio as an evaluation function from an analyzed noise characteristic and a distortion model. The method does not need any transient simulations, reducing the simulation time: a reduction of about 1/48 is achieved. Furthermore low-voltage biasing circuits, such as control circuits, a voltage reference circuit, and a frequency tuning system, are also proposed for higher performance and integration. The control circuits, which provide a dynamic bias current, include a low-voltage current peak detector and measured results of its prototype chip in a 0.35- $\mu m$  CMOS process shows a wide-detection range from a 0.8-V supply. To achieve low-voltage operation a voltage reference circuit uses p-channel MOSFETs in weak inversion region instead of bipolar transistors in conventional bandgap reference circuits. The simulated results show a temperature coefficient of  $-25.5 \text{ ppm/C}^{\circ}$  at 27 C°. The fabricated reference circuit in a 0.18- $\mu m$  CMOS technology outputs a voltage of 0.4 V from a 0.55-V power supply at a room temperature. The frequency tuning system based on a voltage-controlled filter is proposed by replacing a high-gain amplifier with a duty ratio detector and a charge pump circuit for low-voltage operation. Stability analysis of the system is also described.

# Contents

# Chapter

| 1        | Gen  | eral Int | roduction                                                      | 1  |

|----------|------|----------|----------------------------------------------------------------|----|

|          | 1.1  | Backg    | round and Motivation                                           | 1  |

|          | 1.2  | Overv    | iew of the Dissertation                                        | 3  |

| <b>2</b> | Revi | lew of C | Conventional Filters                                           | 5  |

|          | 2.1  | Low-V    | Oltage Filters                                                 | 5  |

|          | 2.2  | Wide-    | Dynamic Range Techniques                                       | 8  |

|          | 2.3  | Comp     | anding Technique                                               | 13 |

| 3        | Synt | hesis N  | lethod of All Low-Voltage CMOS Instantaneous Companding Log    |    |

|          | Dom  | nain Int | egrators                                                       | 15 |

|          | 3.1  | Introd   | uction                                                         | 15 |

|          | 3.2  | Princi   | ple of CMOS Instantaneous Companding Log Domain Integrator     | 16 |

|          | 3.3  | Design   | Considerations                                                 | 17 |

|          |      | 3.3.1    | Expander                                                       | 17 |

|          |      | 3.3.2    | Compressor                                                     | 19 |

|          |      | 3.3.3    | Synthesis Procedures                                           | 21 |

|          |      | 3.3.4    | An Example and Summary of Proposed Design Procedure            | 32 |

|          | 3.4  | Synthe   | esis Examples                                                  | 38 |

|          | 3.5  | Measu    | red Results                                                    | 42 |

|          | 3.6  | Consid   | leration of Log Domain Integrators for Higher-Order Log Domain |    |

|          |      | Filter   | Synthesis                                                      | 46 |

|          | 3.7 | Concl   | usion                                                         | 48 |

|----------|-----|---------|---------------------------------------------------------------|----|

| 4        | CM  | OS Syll | labic Companding Log Domain Filter for Low-Voltage Operation  | 49 |

|          | 4.1 | Introd  | luction                                                       | 49 |

|          | 4.2 | Propo   | sed Low-Voltage Syllabic Companding Integrator in Log Domain  | 50 |

|          |     | 4.2.1   | Dynamically Adjustable Biasing Technique                      | 50 |

|          |     | 4.2.2   | Proposed Low-Voltage Integrator based on Dynamic Biasing      |    |

|          |     |         | Technique                                                     | 52 |

|          | 4.3 | State   | Variable Correction                                           | 54 |

|          |     | 4.3.1   | Current-Type State Variable Correction                        | 54 |

|          |     | 4.3.2   | Voltage-Type State Variable Correction                        | 56 |

|          | 4.4 | Design  | n Examples and Simulated Results                              | 57 |

|          |     | 4.4.1   | Conventional Syllabic Companding Log Domain Filter            | 57 |

|          |     | 4.4.2   | Proposed Syllabic Companding Log Domain Filter Using Current- |    |

|          |     |         | Type State Variable Correction                                | 62 |

|          |     | 4.4.3   | Proposed Syllabic Companding Log Domain Filter Using Voltage- |    |

|          |     |         | Type State Variable Correction                                | 66 |

|          |     | 4.4.4   | Comparison of Two State Variable Correction Methods           | 69 |

|          | 4.5 | Concl   | usion                                                         | 70 |

| <b>5</b> | Opt | imum I  | Design Method of Control Current for Dynamic Range            | 71 |

|          | 5.1 | Introd  | luction                                                       | 71 |

|          | 5.2 | Noise   | and Distortion Modeling                                       | 72 |

|          |     | 5.2.1   | Noise Analysis                                                | 72 |

|          |     | 5.2.2   | Distortion Model                                              | 74 |

|          |     | 5.2.3   | SNDR and Boundary Condition of Control Current                | 75 |

|          | 5.3 | Optin   | num Design Procedure of Control Current                       | 76 |

|          | 5.4 | -       | n Example                                                     | 78 |

|          | 5.5 |         | ssion for control current generation                          | 82 |

|          | 5.6 |         | usion                                                         | 83 |

| 6 | Low   | -Voltage Biasing Circuits and Automatic Frequency Tuning System for | r   |

|---|-------|---------------------------------------------------------------------|-----|

|   | Sylla | bic Companding Log Domain Filters                                   | 85  |

|   | 6.1   | Introduction                                                        | 85  |

|   | 6.2   | Control Current Generator                                           | 86  |

|   |       | 6.2.1 Low-Voltage Current Peak Detector                             | 86  |

|   |       | 6.2.2 Piece-wise Constant Current Generator                         | 90  |

|   | 6.3   | Voltage Reference Circuit under Low-Supply Voltage                  | 93  |

|   | 6.4   | Frequency Tuning System for Log Domain Filter                       | 99  |

|   |       | 6.4.1 Proposed Architecture based on Voltage Controlled filter      | 99  |

|   |       | 6.4.2 Equivalent Linearized Model and Stability                     | 104 |

|   | 6.5   | Conclusion                                                          | 108 |

| 7 | Mea   | sured Results of the Prototype Chips                                | 109 |

|   | 7.1   | Introduction                                                        | 109 |

|   | 7.2   | 5 <sup>th</sup> -order Chebychev Log Domain Filter in 0.35-µm CMOS  | 110 |

|   | 7.3   | 5 <sup>th</sup> -order Chebychev Log Domain Filter in 0.18-µm CMOS  | 119 |

|   | 7.4   | Comparison to Conventional Filters                                  | 128 |

|   | 7.5   | Conclusion                                                          | 128 |

| 8 | Cone  | clusions                                                            | 131 |

# Bibliography

135

# Appendix

| <b>A</b> Log Domain Filter Synthesis and State Variable Correction  | 143 |

|---------------------------------------------------------------------|-----|

| A.1 Synthesis of All-Pole Log Domain Filters                        | 143 |

| A.1.1 Synthesis                                                     | 143 |

| A.1.2 State Variable Correction for Applying to Syllabic Companding |     |

| Technique                                                           | 144 |

| A.2 Synthe | esis of Log Domain Filters with Transmission Zeros            | 145 |

|------------|---------------------------------------------------------------|-----|

| A.2.1      | Synthesis                                                     | 145 |

| A.2.2      | State Variable Correction for Applying to Syllabic Companding |     |

|            | Filters                                                       | 148 |

# Tables

### Table

| 3.1 | Mapping table to replace a voltage buffer and a level shifter          | 27  |

|-----|------------------------------------------------------------------------|-----|

| 3.2 | Connected terminals                                                    | 31  |

| 3.3 | Connections for each drain terminal and prohibited connections in Fig. |     |

|     | 3.10(a)                                                                | 34  |

| 3.4 | The all connections of each terminals for 21 combinations. $\ldots$ .  | 37  |

| 3.5 | Characteristics of all the generated CMOS log-domain integrators with  |     |

|     | a 100% negative feedback applied                                       | 39  |

| 3.5 | Characteristics of all the generated CMOS log-domain integrators with  |     |

|     | a 100% negative feedback applied. (continued)                          | 40  |

| 3.6 | Summary of measured filter characteristics                             | 46  |

| 5.1 | Coefficients in Eq. $(5.5)$                                            | 80  |

| 6.1 | Design parameters for voltage reference circuit.                       | 96  |

| 7.1 | Transconductance and capacitances in a log domain filter core          | 110 |

| 7.2 | Summary of measured filter characteristics                             | 118 |

| 7.3 | Comparison with other low-voltage filters                              | 118 |

| 7.4 | Performance summary.                                                   | 127 |

| 7.5 | Comparison to other recently published filters                         | 129 |

# Figures

# Figure

| Technology road map for semiconductor in the future: relation among            |                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| technology node, supply voltage $V_{DD}$ , and threshold voltage $V_{th}$ [1]. | 2                                                                                                                                                                                                                                                           |

| Operational transconductance amplifiers (OTAs) and an integrator:              |                                                                                                                                                                                                                                                             |

| (a) a conventional differential amplifier as OTA, (b) a 0.5-V OTA, and         |                                                                                                                                                                                                                                                             |

| (c) a 0.5-V integrator [16]                                                    | 6                                                                                                                                                                                                                                                           |

| Low-voltage CMOS log domain integrator [33]                                    | 7                                                                                                                                                                                                                                                           |

| Relation between signal-to-noise-plus-distortion ratio (SNDR) and dy-          |                                                                                                                                                                                                                                                             |

| namic range (DR).                                                              | 9                                                                                                                                                                                                                                                           |

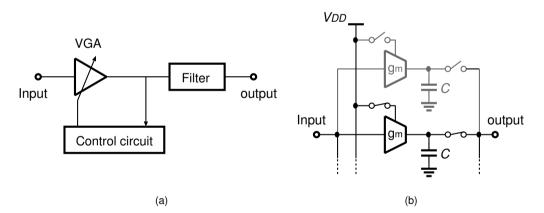

| Techniques for wide-dynamic range analog signal processing: (a) a filter       |                                                                                                                                                                                                                                                             |

| with an automatic gain controlled (AGC) circuit and (b) an integrator          |                                                                                                                                                                                                                                                             |

| in a filter using dynamic impedance scaling technique                          | 9                                                                                                                                                                                                                                                           |

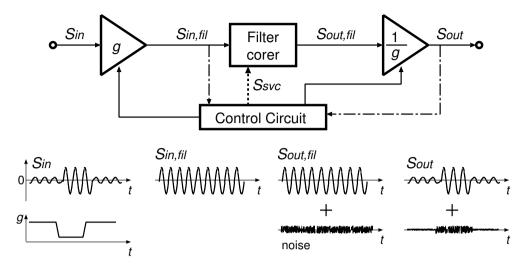

| A filter using the companding technique and its conceptual waveforms.          | 10                                                                                                                                                                                                                                                          |

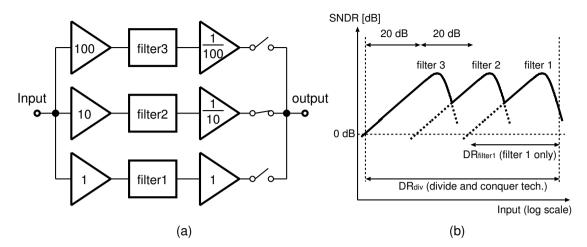

| Divide-and-conquer technique: (a) the block diagram and (b) its signal-        |                                                                                                                                                                                                                                                             |

| to-noise-plus-distortion ratio (SNDR)                                          | 11                                                                                                                                                                                                                                                          |

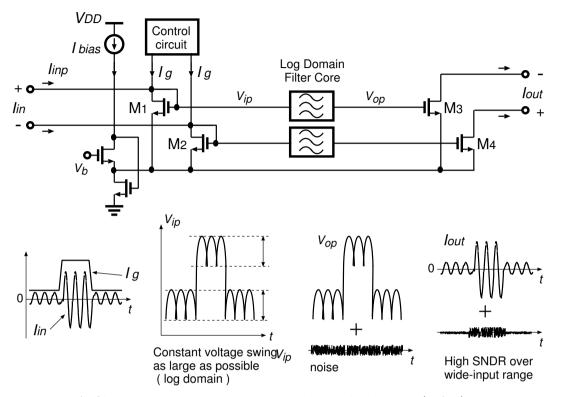

| A filter using the dynamically adjustable biasing (DAB) technique and          |                                                                                                                                                                                                                                                             |

| its conceptual waveforms.                                                      | 12                                                                                                                                                                                                                                                          |

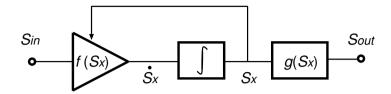

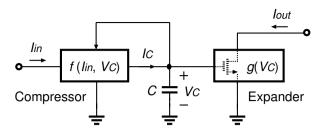

| Principle of <i>instantaneous</i> companding integrator                        | 13                                                                                                                                                                                                                                                          |

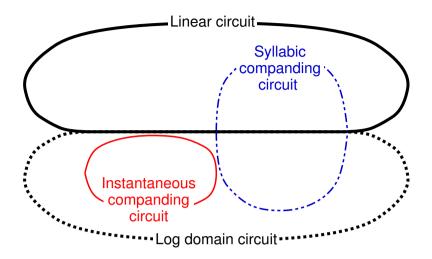

| Relation among linear circuit, log domain circuit, instantaneous com-          |                                                                                                                                                                                                                                                             |

| panding circuit, and syllabic companding circuit                               | 14                                                                                                                                                                                                                                                          |

|                                                                                | technology node, supply voltage $V_{DD}$ , and threshold voltage $V_{th}$ [1]<br>Operational transconductance amplifiers (OTAs) and an integrator:<br>(a) a conventional differential amplifier as OTA, (b) a 0.5-V OTA, and<br>(c) a 0.5-V integrator [16] |

| 3.1  | CMOS instantaneous companding log domain integrator with a MOS-                                                              |    |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

|      | FET in weak inversion region as an expander                                                                                  | 16 |

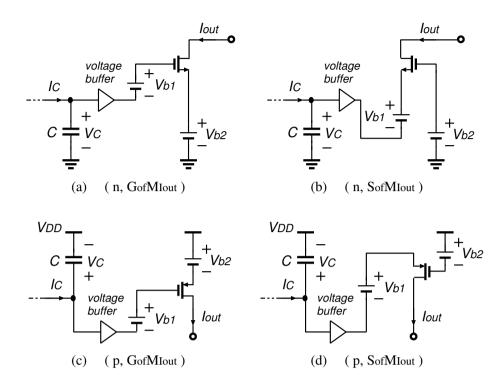

| 3.2  | All expander configurations expressed as $(TypeM_{exp}, TCV_C)$                                                              | 18 |

| 3.3  | Translinear loop (TL).                                                                                                       | 19 |

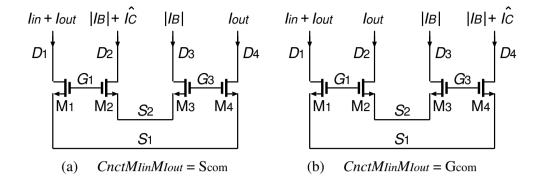

| 3.4  | Current allocations in a TL for a compressor.                                                                                | 20 |

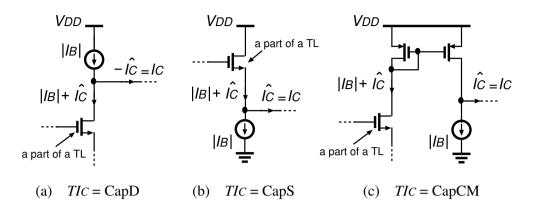

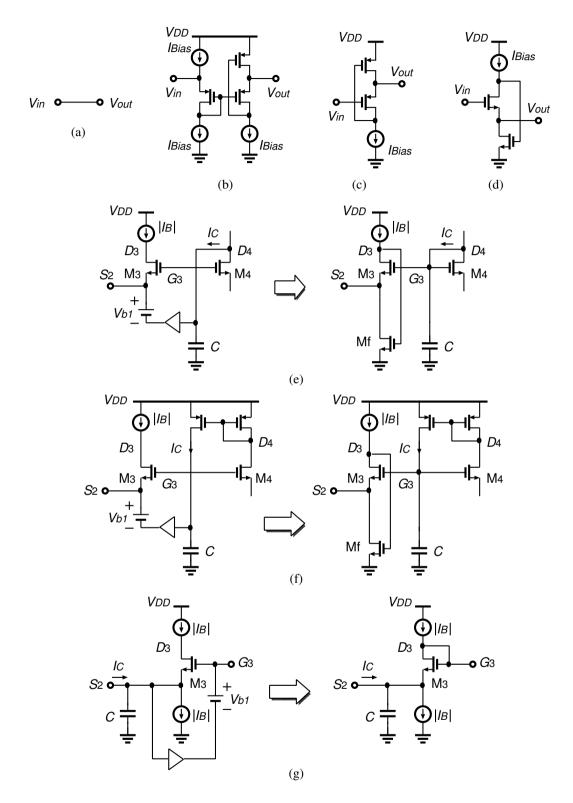

| 3.5  | Realization of a capacitor current $I_C$                                                                                     | 21 |

| 3.6  | Realization of circuits represented as $(TypeM_{exp}, TCV_C, TI_C) = (n,$                                                    |    |

|      | $G_{of}M_{I_{out}}, CapS).$                                                                                                  | 23 |

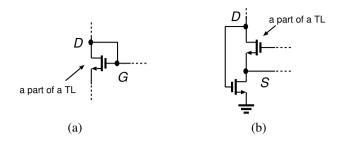

| 3.7  | Implementation of a voltage buffer and a level shifter                                                                       | 25 |

| 3.8  | Feedback connection to settle a drain voltage                                                                                | 28 |

| 3.9  | Circuits for a floating node.                                                                                                | 29 |

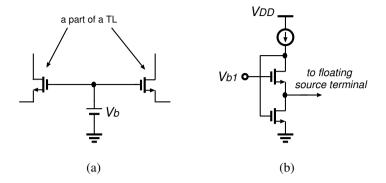

| 3.10 | Design examples.                                                                                                             | 33 |

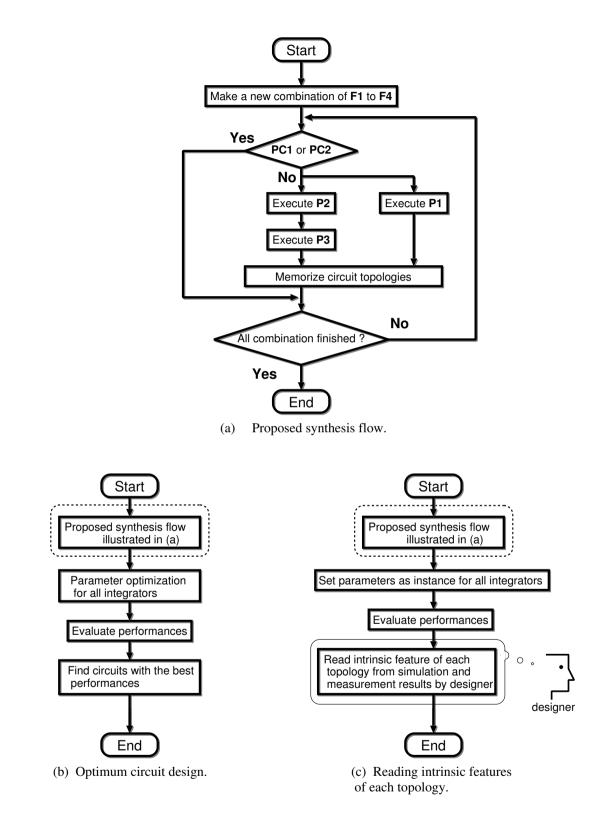

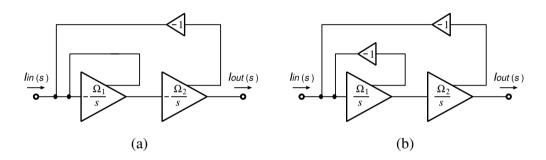

| 3.11 | Proposed synthesis flow and its application examples                                                                         | 35 |

| 3.12 | Circuit expressed by (p, $G_{of}M_{I_{out}}$ , $G_{com}$ , CapS, 1)                                                          | 41 |

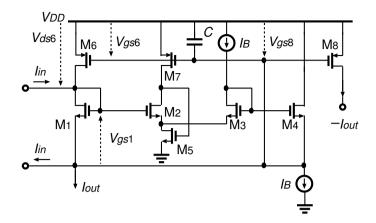

| 3.13 | Two integrators for $2^{nd}$ -order Butterworth low-pass filters                                                             | 42 |

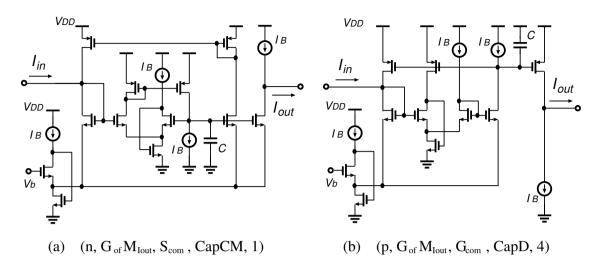

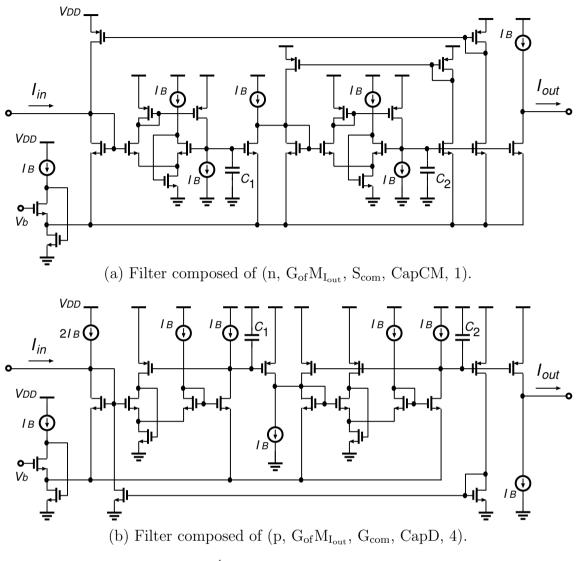

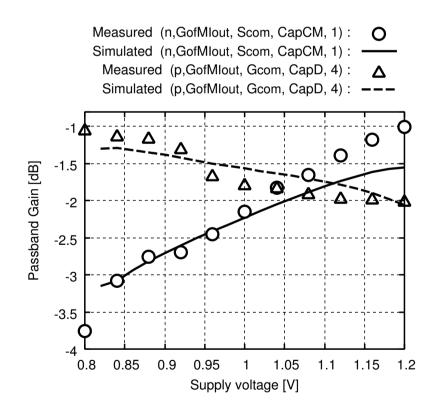

| 3.14 | $2^{\rm nd}\text{-}{\rm order}$ low-pass filter structures: (a) for (n, $G_{\rm of}M_{\rm I_{out}},S_{\rm com},{\rm CapCM},$ |    |

|      | 1) and (b) for (p, $G_{of}M_{I_{out}}$ , $G_{com}$ , CapD, 4).                                                               | 42 |

| 3.15 | $2^{nd}$ -order Butterworth low-pass filters                                                                                 | 43 |

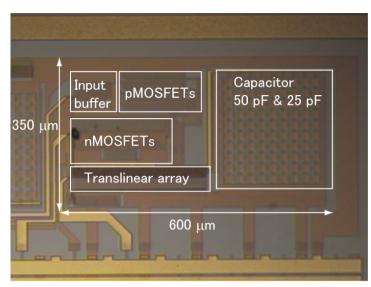

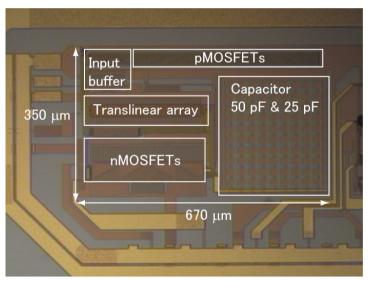

| 3.16 | Chip microphotographs of $2^{nd}$ -order Butterworth low-pass filters                                                        | 44 |

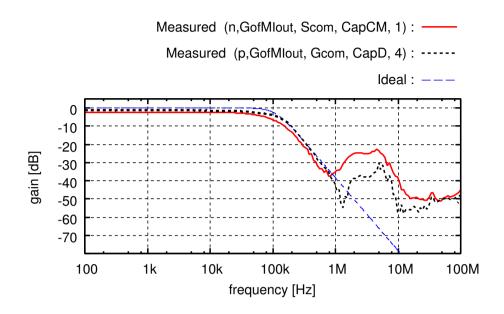

| 3.17 | Frequency characteristics.                                                                                                   | 45 |

| 3.18 | Sensitivity of DC gain for variation in a power supply voltage                                                               | 45 |

| 3.19 | Redrawn block diagram of instantaneous companding log domain in-                                                             |    |

|      | tegrator from Fig. 3.1                                                                                                       | 47 |

| 3.20 | Differential input log domain integrator from (n, $G_{of}M_{I_{out}}$ , $S_{com}$ , CapD,                                    |    |

|      | 1) and (n, $G_{of}M_{I_{out}}$ , $S_{com}$ , CapCM, 1)                                                                       | 47 |

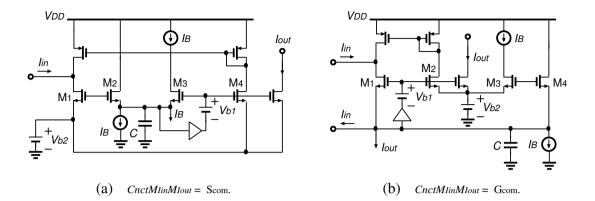

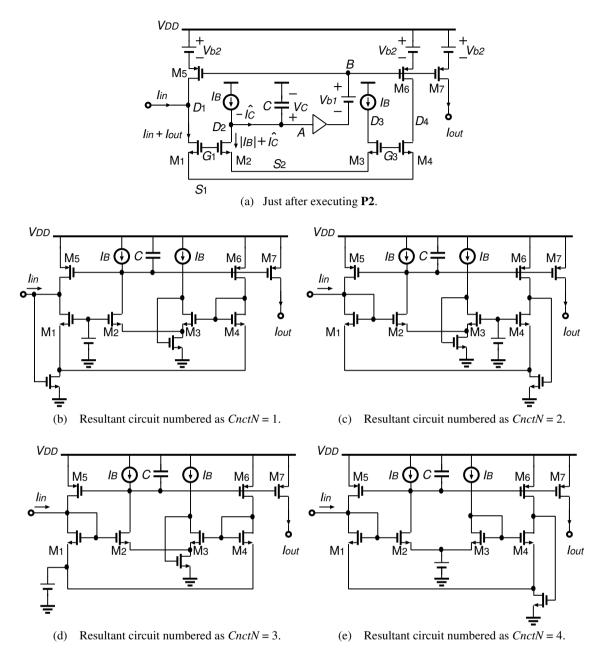

| 4.1  | Example circuitry of dynamically adjustable biasing (DAB) $\log$ domain                                                      |    |

|      | filters                                                                                                                      | 50 |

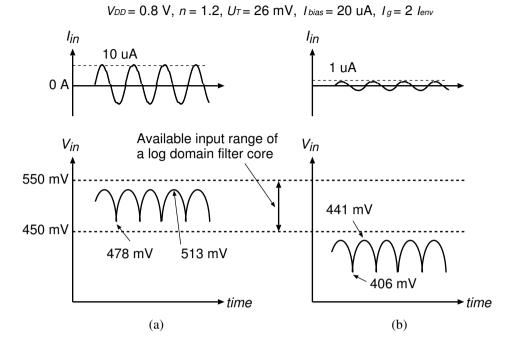

| 4.2  | Input voltage $V_{in}$ of a log domain filter core and its available input range                                      |    |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

|      | in conventional DAB-based circuit when (a) $I_{in}$ is a 10- $\mu$ A sinusoidal                                       |    |

|      | current and (b) a 1- $\mu$ A one                                                                                      | 52 |

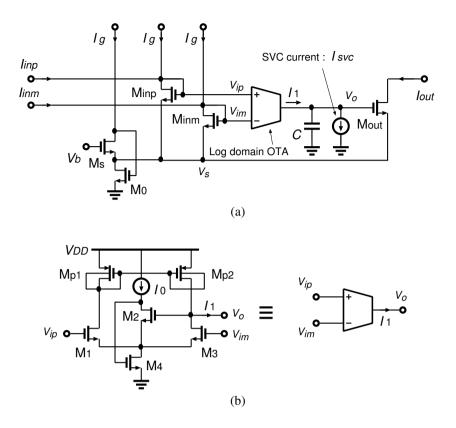

| 4.3  | Proposed DAB-based integrator                                                                                         | 53 |

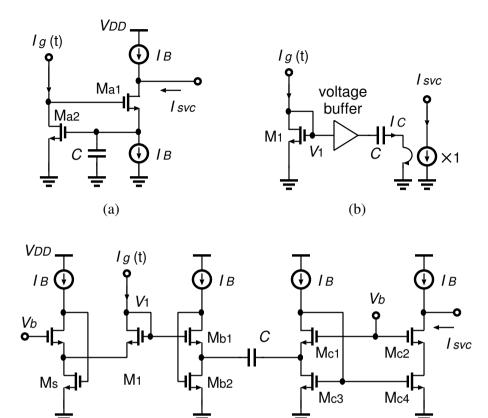

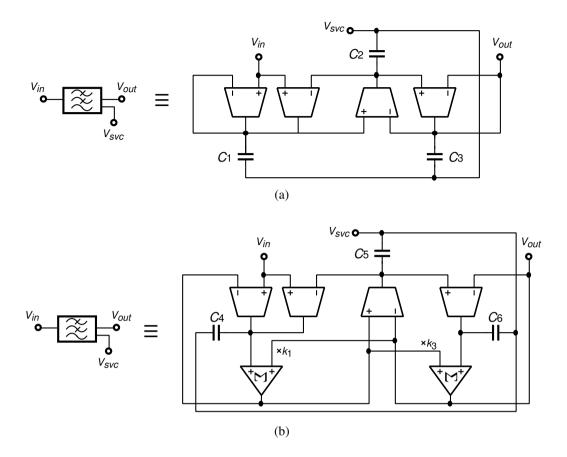

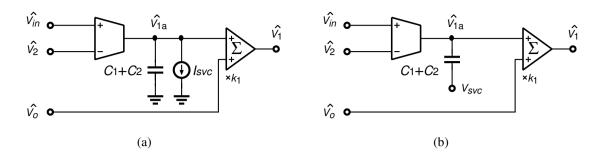

| 4.4  | State variable correction (SVC) circuits: (a) conventional circuitry, (b)                                             |    |

|      | SVC model, and (c) proposed circuitry                                                                                 | 55 |

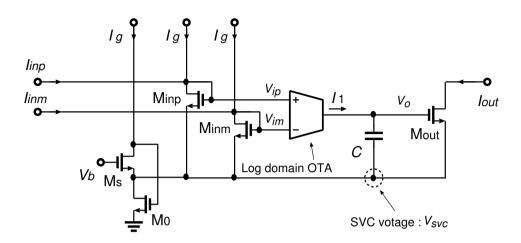

| 4.5  | Voltage-type SVC method                                                                                               | 56 |

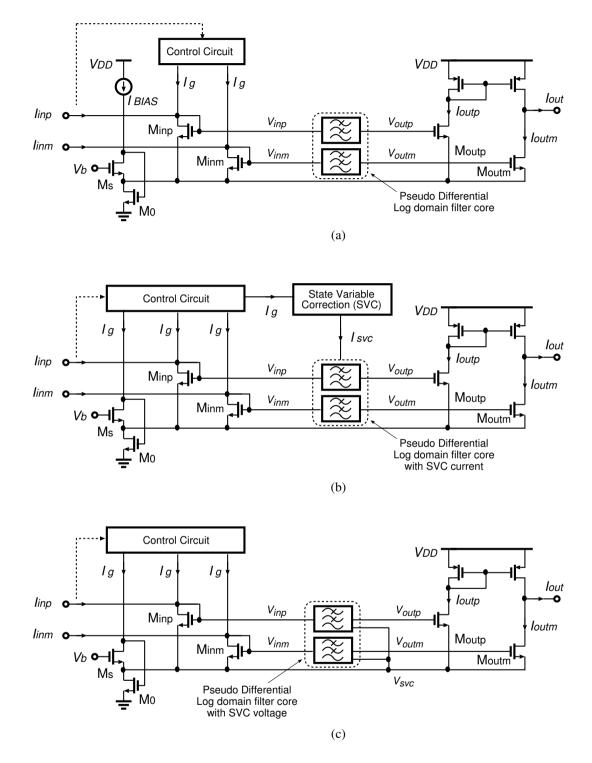

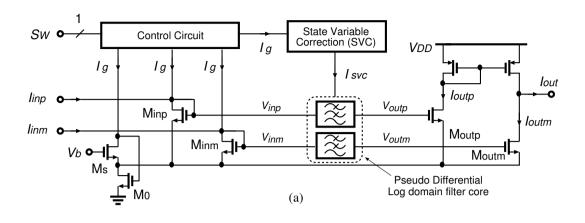

| 4.6  | The overall syllabic companding log domain filters using (a) conven-                                                  |    |

|      | tional dynamically adjustable biasing (DAB) technique, (b) proposed                                                   |    |

|      | low-voltage DAB technique with current-type SVC, and (c) with voltage-                                                |    |

|      | type SVC                                                                                                              | 58 |

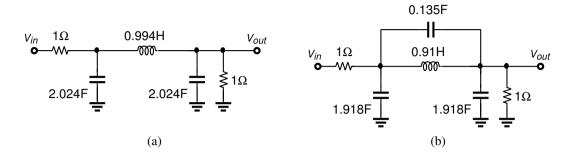

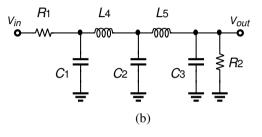

| 4.7  | RLC prototype ladders: (a) $3^{rd}$ -order Chebychev filter with 1-dB pass-                                           |    |

|      | band ripple and (b) $3^{rd}$ -order elliptic filter with 1-dB passband ripple                                         |    |

|      | and 40-dB stopband attenuation from 2.5 Hz                                                                            | 59 |

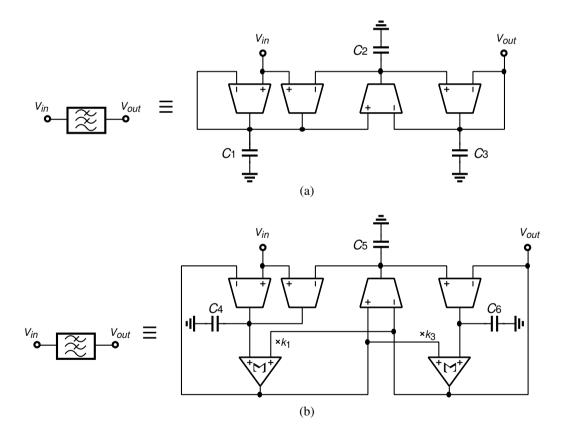

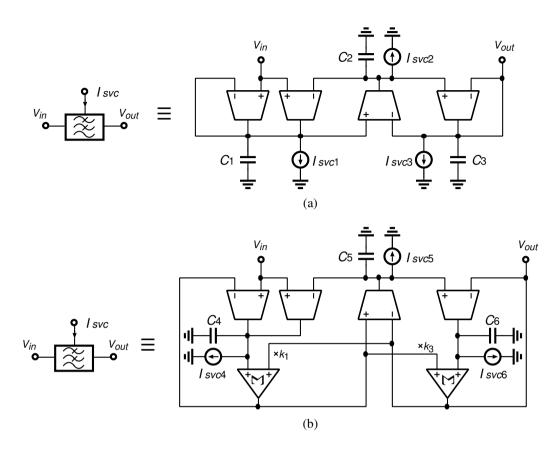

| 4.8  | Log domain filter cores for the conventional DAB-based filters: (a)                                                   |    |

|      | $3^{\rm rd}\text{-}{\rm order}$ Chebychev (all pole) low-pass filter and (b) $3^{\rm rd}\text{-}{\rm order}$ elliptic |    |

|      | (with transmission zeros) low-pass filter. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                               | 59 |

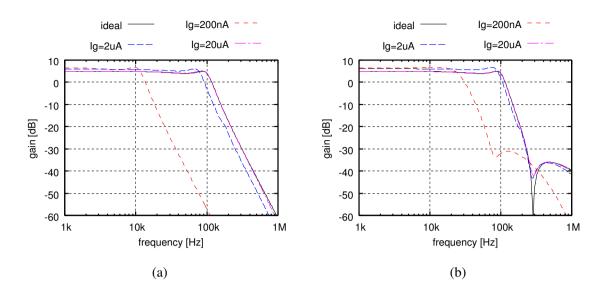

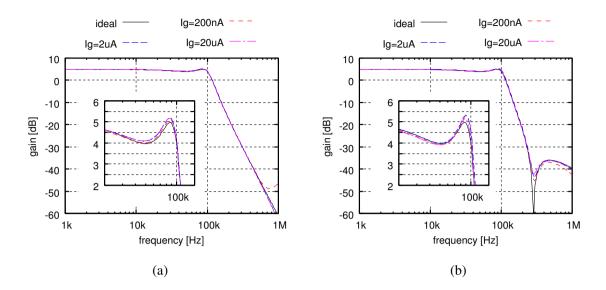

| 4.9  | Frequency response of the conventional DAB-based filters: (a) $3^{rd}$ -                                              |    |

|      | order Chebychev filter and (b) $3^{rd}$ -order elliptic filter                                                        | 60 |

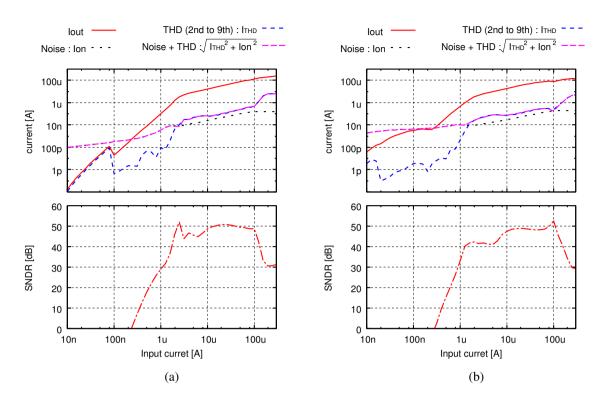

| 4.10 | Dynamic range characteristics at a 100-kHz tone for the conventional                                                  |    |

|      | DAB-based filters: (a) $3^{rd}$ -order Chebychev filter and (b) $3^{rd}$ -order                                       |    |

|      | elliptic filter                                                                                                       | 61 |

| 4.11 | Log domain filter cores for the proposed low-voltage DAB-based filters                                                |    |

|      | using current-type SVC: (a) $3^{\rm rd}$ -order Chebychev (all pole) low-pass                                         |    |

|      | filter and (b) 3 <sup>rd</sup> -order elliptic (with transmission zeros) low-pass filter.                             | 62 |

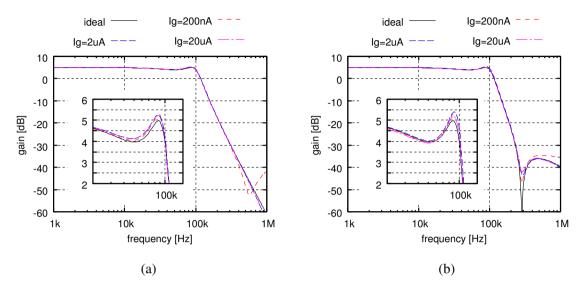

| 4.12 | Frequency response of the proposed DAB-based filters using current-                                                   |    |

|      | type SVC: (a) 3 <sup>rd</sup> -order Chebychev filter and (b) 3 <sup>rd</sup> -order elliptic filter.                 | 63 |

| 4.13 | Dynamic range characteristics at a 100-kHz tone for the proposed                                      |    |

|------|-------------------------------------------------------------------------------------------------------|----|

|      | DAB-based filters using current-type SVC: (a) 3 <sup>rd</sup> -order Chebychev                        |    |

|      | filter and (b) $3^{rd}$ -order elliptic filter                                                        | 64 |

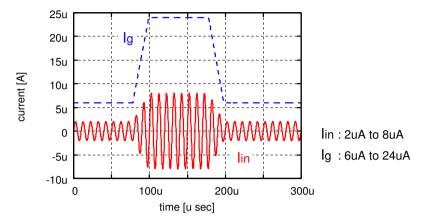

| 4.14 | Input current $I_{in}$ and a control current $I_g$ for transient simulations.                         | 65 |

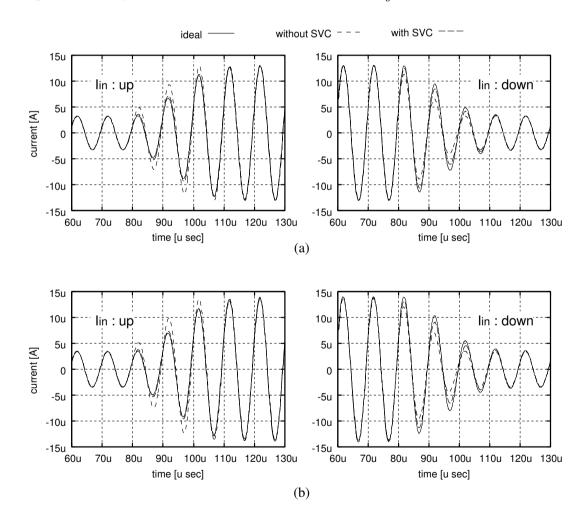

| 4.15 | Output current $I_{out}$ when the envelope changes: (a) Chebychev filter                              |    |

|      | and (b) elliptic filter                                                                               | 65 |

| 4.16 | Log domain filter cores for the proposed low-voltage DAB-based filters                                |    |

|      | using voltage-type SVC: (a) 3 <sup>rd</sup> -order Chebychev (all pole) low-pass                      |    |

|      | filter and (b) 3 <sup>rd</sup> -order elliptic (with transmission zeros) low-pass filter.             | 66 |

| 4.17 | Frequency response of the proposed DAB-based filters using voltage-                                   |    |

|      | type SVC: (a) 3 <sup>rd</sup> -order Chebychev filter and (b) 3 <sup>rd</sup> -order elliptic filter. | 67 |

| 4.18 | Dynamic range characteristics at a 100-kHz tone for the proposed                                      |    |

|      | DAB-based filters using voltage-type SVC: (a) 3 <sup>rd</sup> -order Chebychev                        |    |

|      | filter and (b) $3^{rd}$ -order elliptic filter                                                        | 67 |

| 4.19 | Output current $I_{out}$ when the envelope changes: (a) Chebychev filter                              |    |

|      | and (b) elliptic filter                                                                               | 68 |

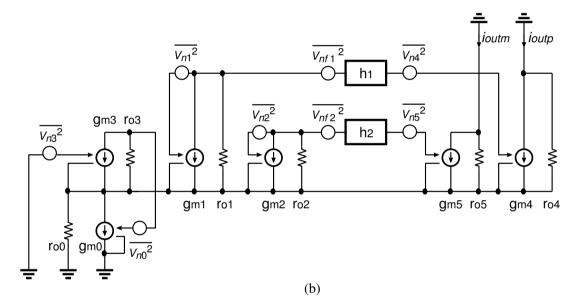

| 5.1  | Low-voltage syllabic companding log domain filter (DAB-based filter):                                 |    |

|      | (a) circuitry and (b) small signal model for noise analysis. $\ldots$ .                               | 73 |

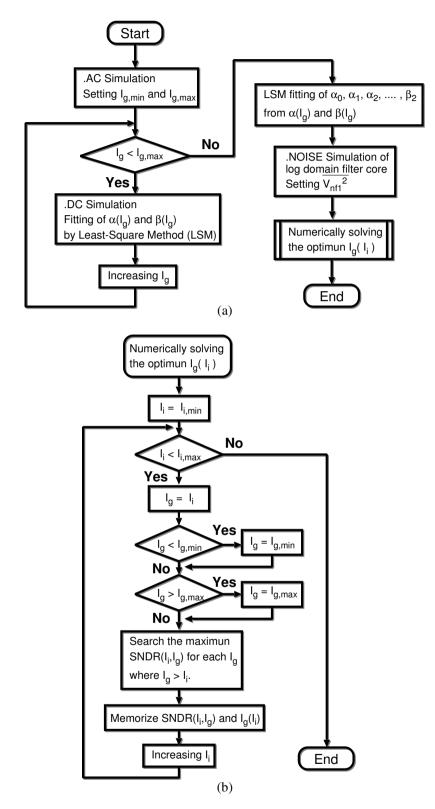

| 5.2  | (a) Procedure for an optimum control current design and (b) numeri-                                   |    |

|      | cally method for finding a locus of an optimum control current. $\ . \ .$                             | 77 |

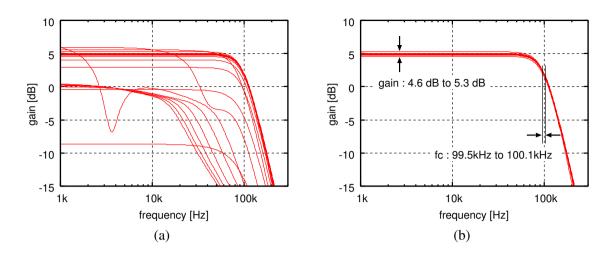

| 5.3  | Frequency responses for each $I_g$ . (a) $I_g$ is 1 nA to 1 mA and (b) $I_g$ :                        |    |

|      | 30 nA to 300 $\mu$ A                                                                                  | 78 |

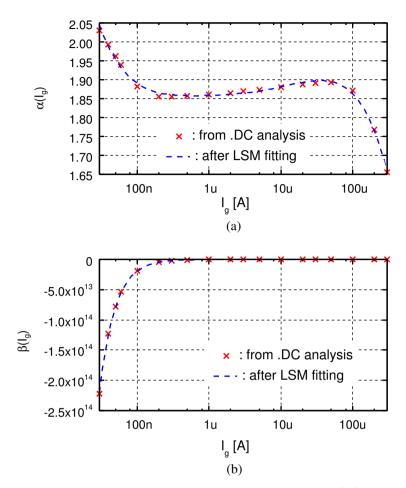

| 5.4  | Coefficients $\alpha$ and $\beta$ for each $I_g(I_i)$                                                 | 79 |

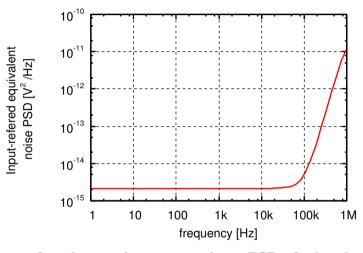

| 5.5  | Input-referred equivalent noise voltage PSD of a log domain filter core.                              | 80 |

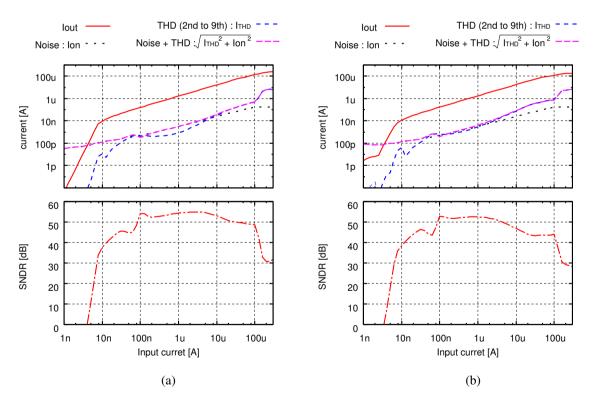

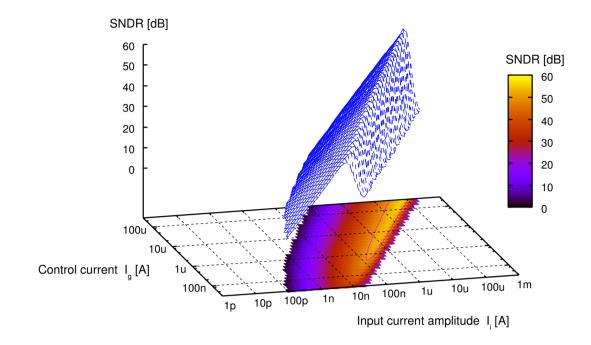

| 5.6  | SNDR from transient-based simulation results                                                          | 81 |

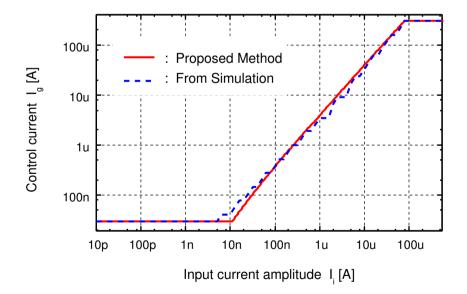

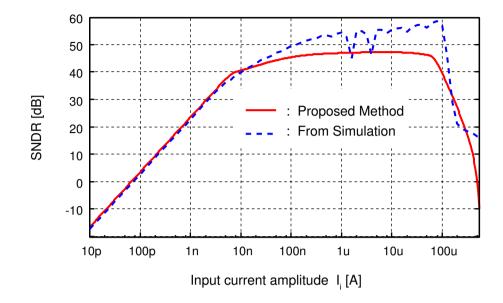

| 5.7  | Analytical optimum control current by proposed method and practical                                   |    |

|      | optimum control current based on transient simulations                                                | 81 |

| 5.8  | SNDRs of the filter by using each control current in Fig. 5.7                                         | 82 |

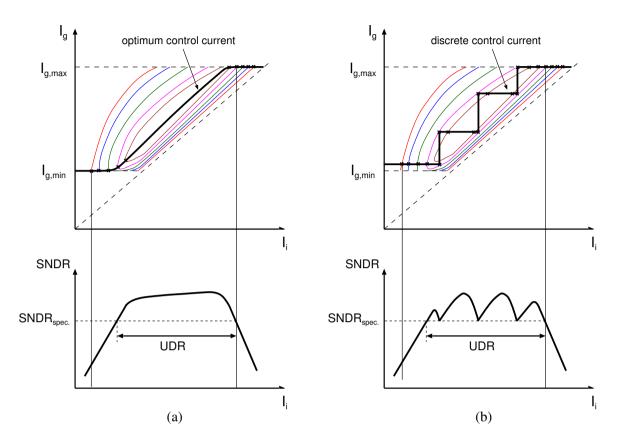

| 5.9  | SNDRs at different locus of control current: (a) optimum and (b) discrete.                            | 83 |

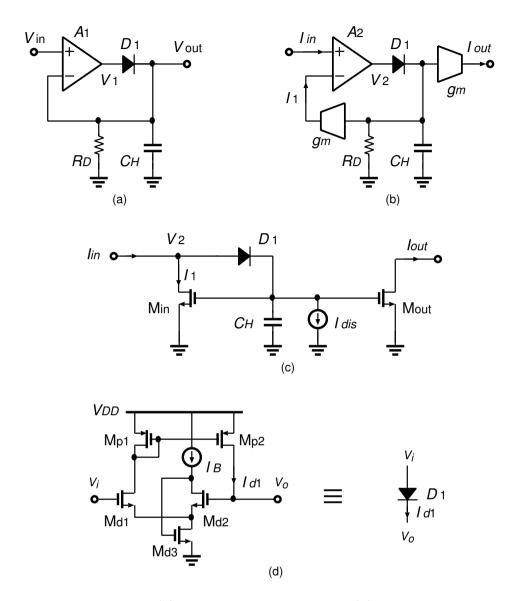

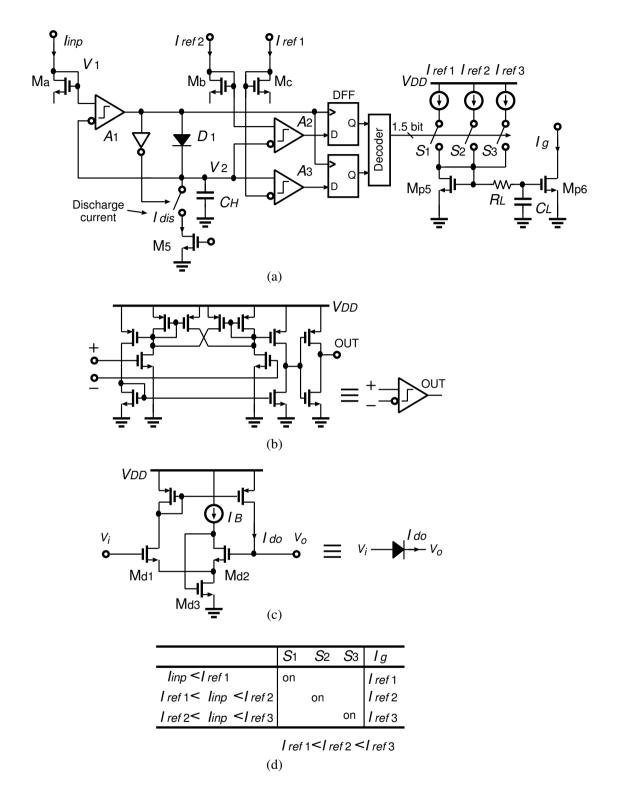

| 6.1  | Peak detector. (a) Voltage-mode approach. (b) Current-mode ap-                                 |

|------|------------------------------------------------------------------------------------------------|

|      | proach. (c) CMOS implementation of (b). (d) Low-voltage equivalent                             |

|      | diode with a zero drop voltage between $V_i$ and $V_o$                                         |

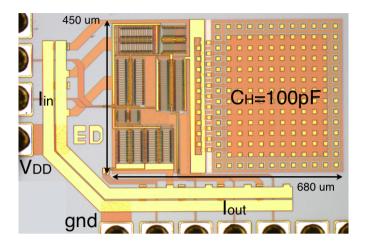

| 6.2  | Microphotograph of the proposed peak detector                                                  |

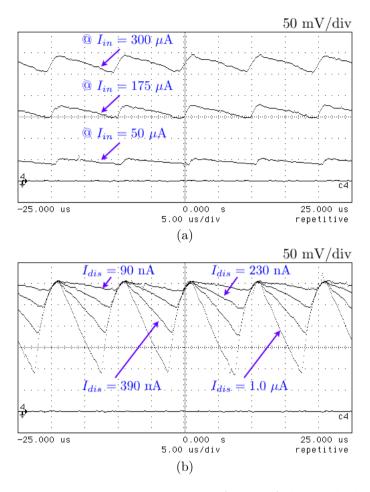

| 6.3  | The measured output current waveforms of the peak detector at a 100-                           |

|      | kHz sinusoidal input current. (a) The waveforms for different input                            |

|      | current amplitude and (b) discharge current $I_{dis}$                                          |

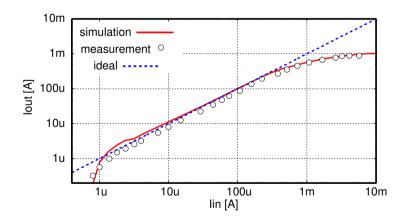

| 6.4  | Input current amplitude v.s. peak value of output current 89                                   |

| 6.5  | Piece-wide constant control current generator: (a) three-value quan-                           |

|      | tized peak detector, (b) comparator circuit $A_1$ , $A_2$ and $A_3$ , (c) equiv-               |

|      | alent diode circuit with a high-input impedance, and diagram for the                           |

|      | switches                                                                                       |

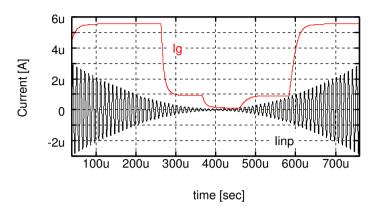

| 6.6  | A response of the control current $I_g$ for the input current $I_{inp}$ with                   |

|      | envelope sweep                                                                                 |

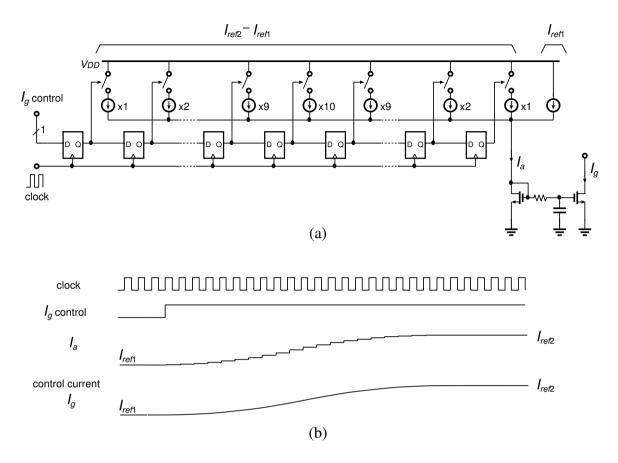

| 6.7  | An output stage of the control current generator for smooth change of                          |

|      | $I_g$ . (a) the circuitry and (b) its timing diagram. $\ldots \ldots \ldots \ldots \ldots $ 93 |

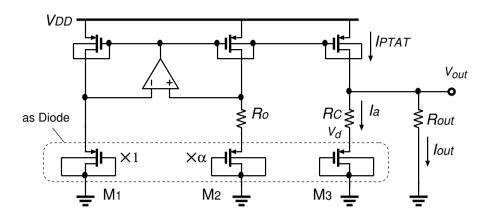

| 6.8  | Low-voltage reference circuit                                                                  |

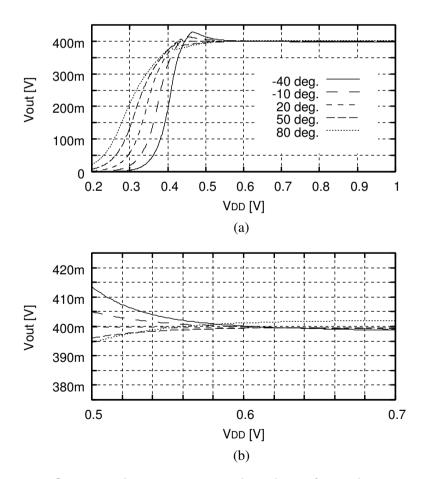

| 6.9  | Output voltage versus supply voltage for each temperature 96                                   |

| 6.10 | Temperature variation: (a) output voltage and (b) temperature coeffi-                          |

|      | cient (TC)                                                                                     |

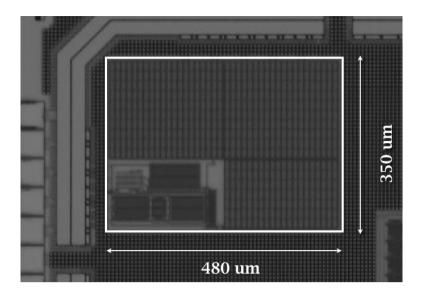

| 6.11 | Chip microphotograph of the voltage reference circuit                                          |

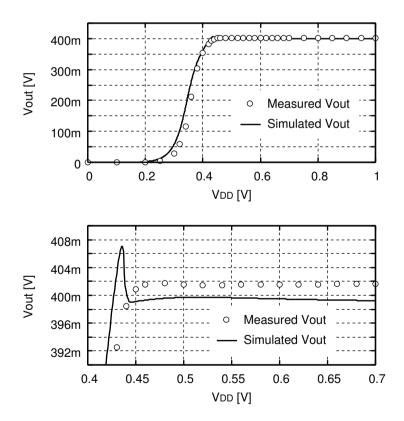

| 6.12 | Measured result of the voltage reference circuit under room temperature. 98                    |

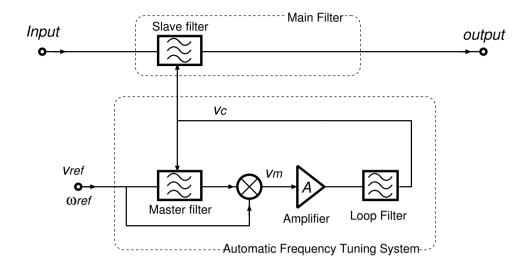

| 6.13 | A frequency tuning system based on voltage-controlled filter (VCF) 99                          |

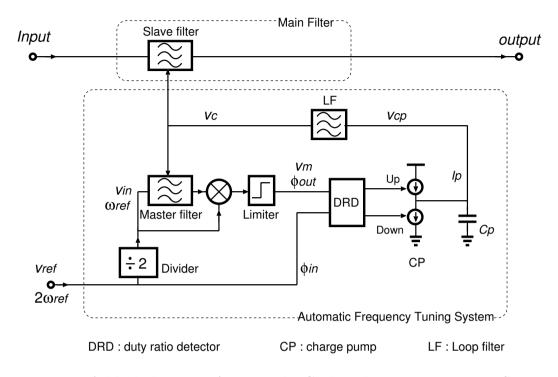

| 6.14 | A block diagram of proposed VCF-based Frequency Tuning System 101                              |

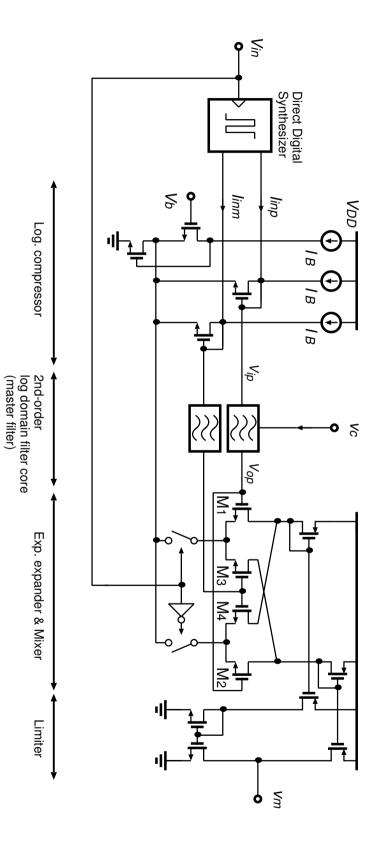

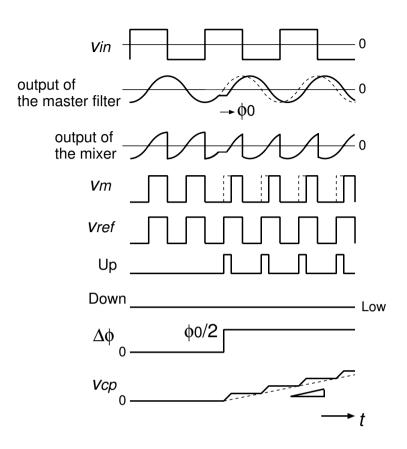

| 6.15 | A master filter and a mixer including exponential expander 102                                 |

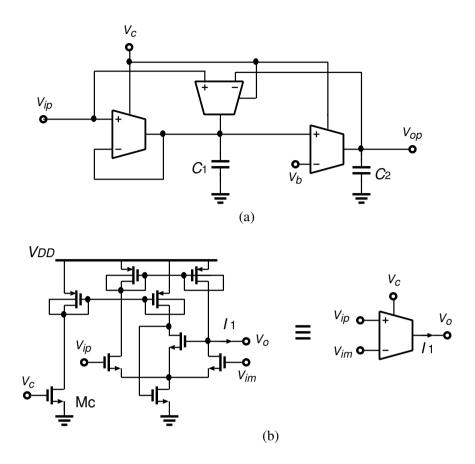

| 6.16 | A second-order low-pass log domain filter core (one half only): (a)                            |

|      | configuration and (b) a tunable log domain OTA                                                 |

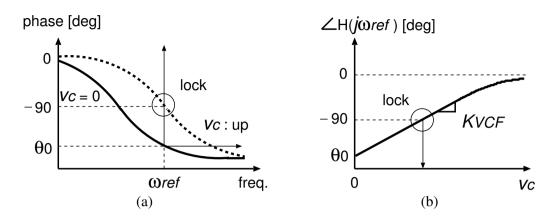

| 6.17 | (a) phase response of the master filter $H_{mst}(s)$ and (b) relation between                  |

|      | frequency shift and control voltage $V_c$                                                      |

| 6.18 | Control voltage and phase behavior when a cutoff frequency $f_c$ changes   | .105 |

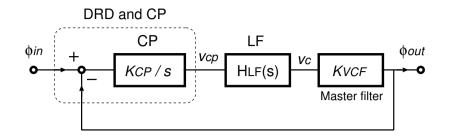

|------|----------------------------------------------------------------------------|------|

| 6.19 | Linearized mode of the proposed frequency tuning system                    | 106  |

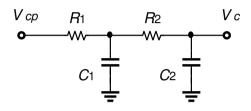

| 6.20 | Loop filter $H_{LP}(s)$                                                    | 106  |

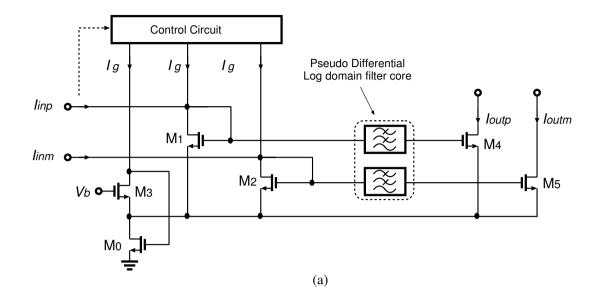

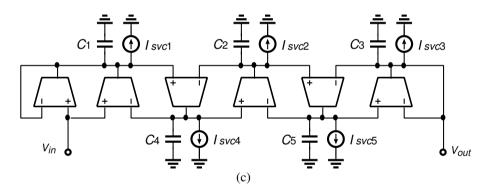

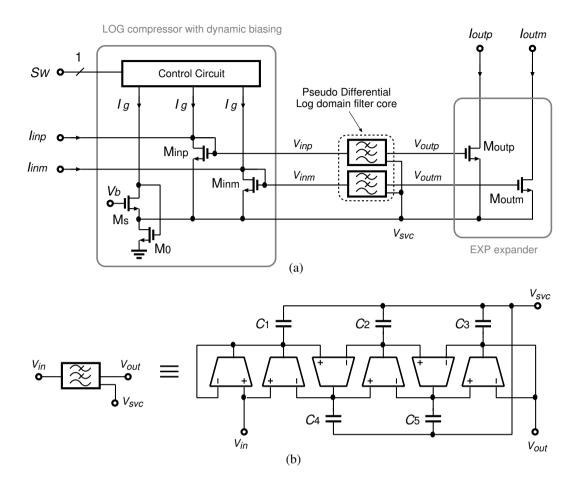

| 7.1  | Syllabic-companding log domain fifth-order Chebychev low-pass filter:      |      |

|      | (a) overall circuity, (b) RLC prototype filter, and (c) log domain filter  |      |

|      | core (one half only).                                                      | 111  |

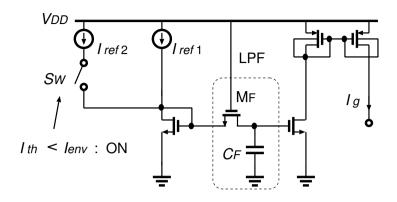

| 7.2  | Control current $I_g$ generator                                            | 112  |

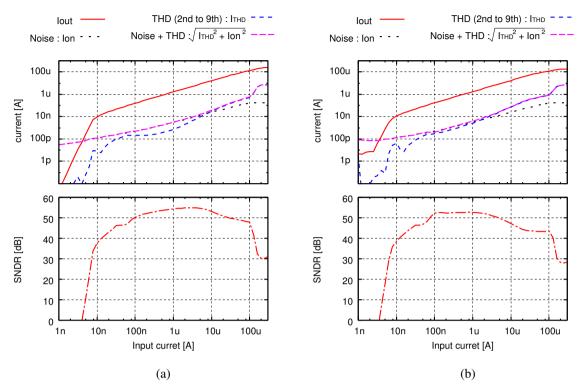

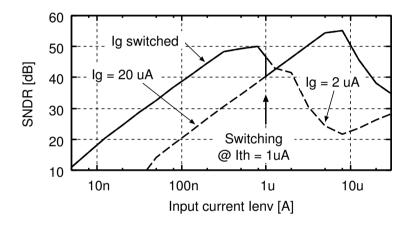

| 7.3  | Simulation results of signal-to-noise-plus-distortion ratios (SNDRs) for   |      |

|      | a 100-kHz sinusoidal input current.                                        | 112  |

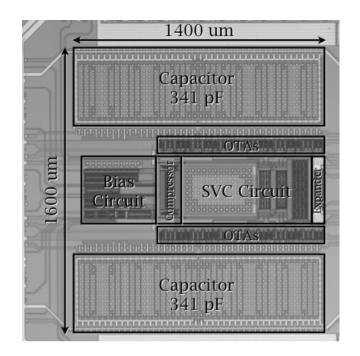

| 7.4  | Chip microphotograph                                                       | 113  |

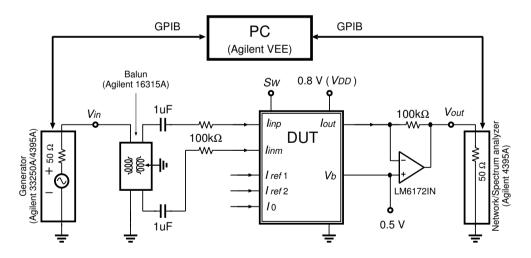

| 7.5  | Measurement setup                                                          | 113  |

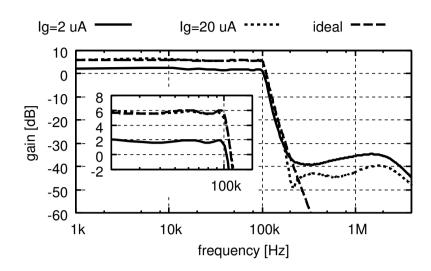

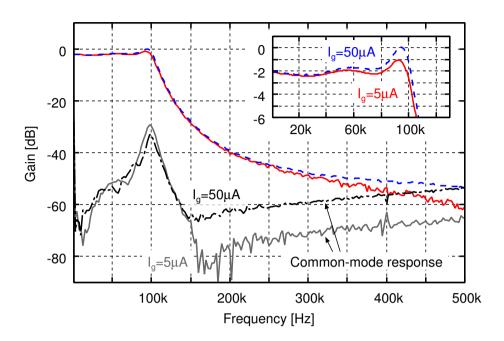

| 7.6  | Measured frequency responses                                               | 114  |

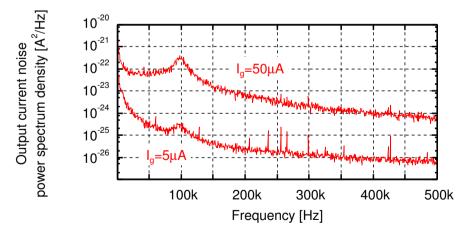

| 7.7  | Measured output noise current power spectrum density                       | 114  |

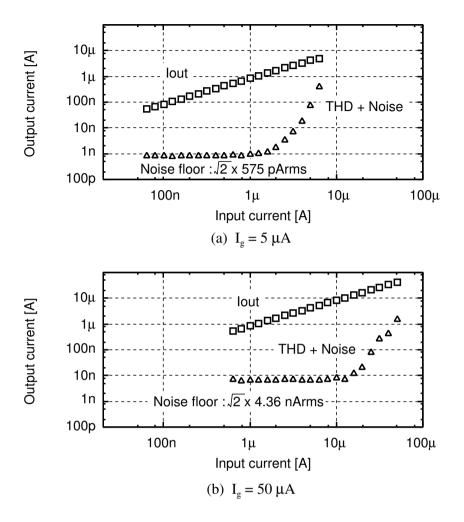

| 7.8  | Output current components with a 100-kHz sinusoidal input current          |      |

|      | amplitude varied.                                                          | 115  |

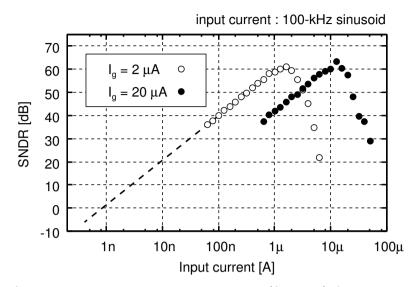

| 7.9  | Signal to noise plus distortion ratios for a 100-kHz sinusoidal input      |      |

|      | current                                                                    | 116  |

| 7.10 | Output current waveforms with ${\cal I}_g$ varied when a 20-kHz sinusoidal |      |

|      | input current applied                                                      | 117  |

| 7.11 | Syllabic-companding log domain fifth-order Chebychev low-pass filter       |      |

|      | using voltage-type SVC method: (a) overall circuity, (b) log domain        |      |

|      | filter core (one half only).                                               | 119  |

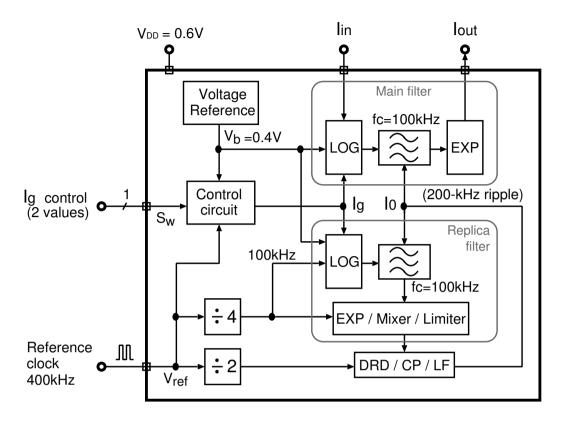

| 7.12 | Overall block diagram of the prototype fitter chip                         | 120  |

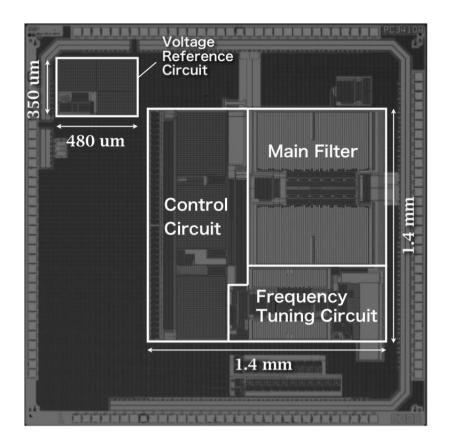

| 7.13 | Chip microphotograph of the prototype filter in 0.18- $\mu m$ CMOS         | 122  |

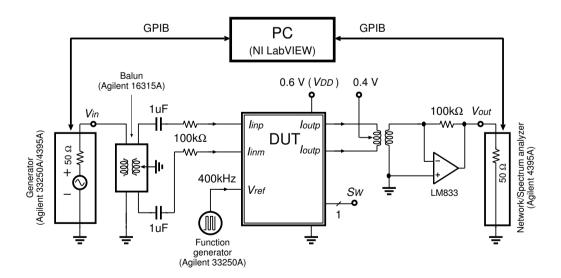

| 7.14 | Measurement setup                                                          | 122  |

| 7.15 | Frequency response and common-mode response at different control           |      |

|      | currents                                                                   | 123  |

| 7.16 | Phase and group delay characteristics.                                     | 124  |

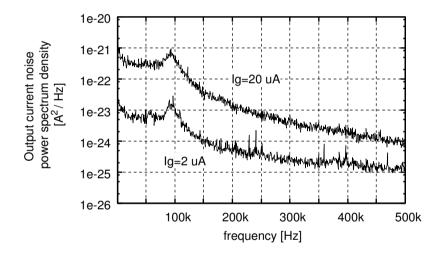

| 7.17 | Output current noise power spectrum density at different control cur-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | rents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 124  |

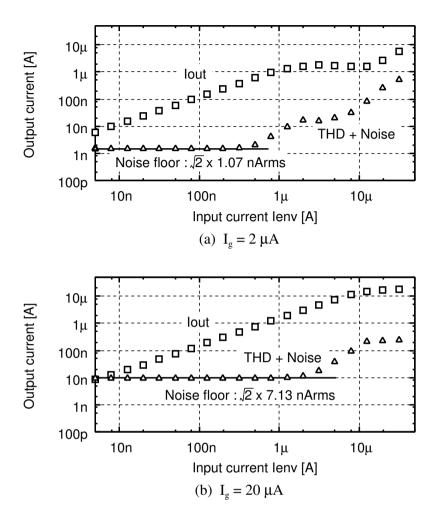

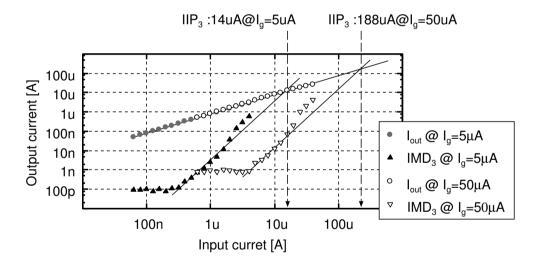

| 7.18 | Output current components with a 100-kHz sinusoidal input current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|      | amplitude varied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 125  |

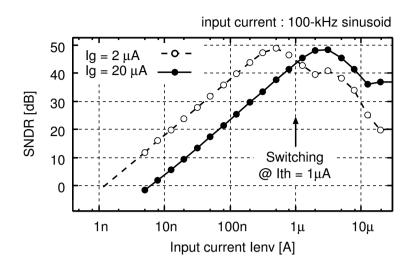

| 7.19 | Signal-to-noise-plus-distortion ratios (SNDRs) for a 100-kHz sinusoidal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|      | input current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 126  |

| 7.20 | Fundamental components and third-order intermodulated distortions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|      | $(IMD_3)$ and third-order in-band input-refereed intercept point $(IIP_3)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|      | for each $I_g$ where 40-kHz and 80-kHz tones are applied                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 126  |

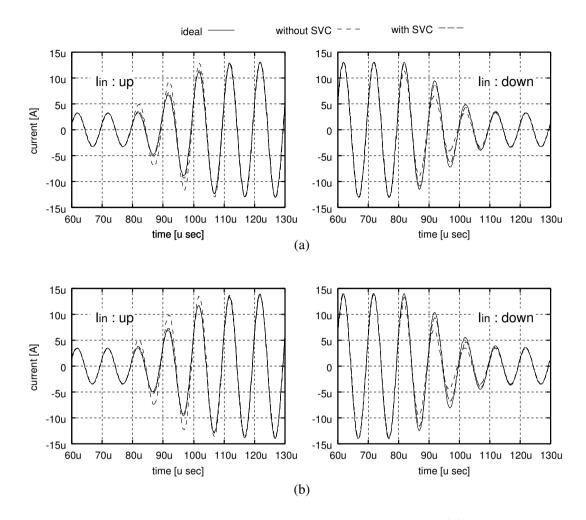

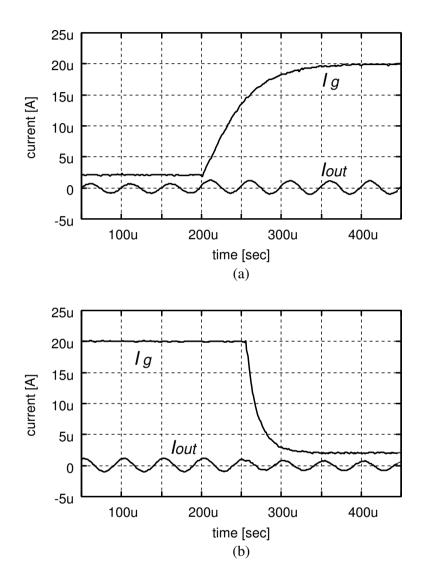

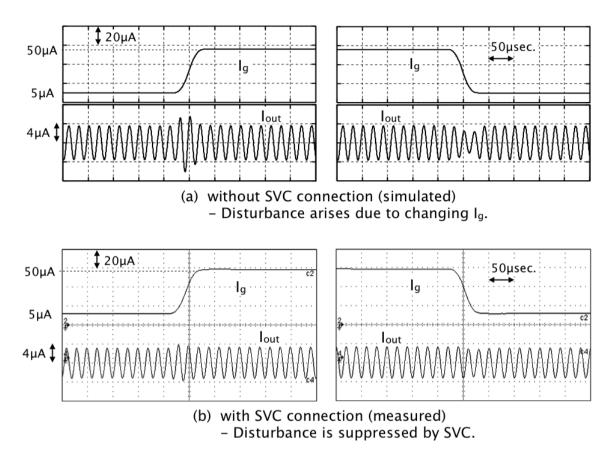

| 7.21 | Transient response when the control current $I_g$ changes: (a) simulated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|      | results without SVC and (b) measured results with SVC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 127  |

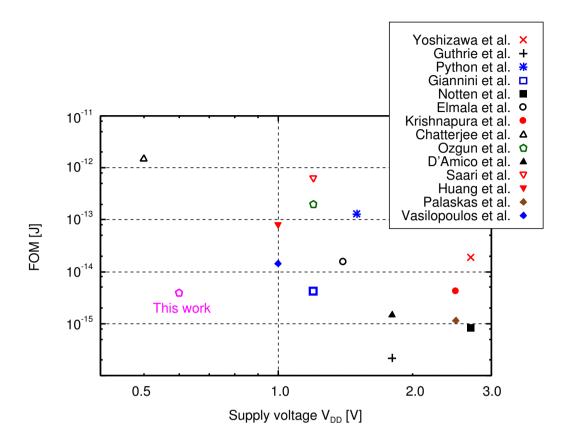

| 7.22 | Comparison to other recently published filters: $V_{DD}$ vs FOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 130  |

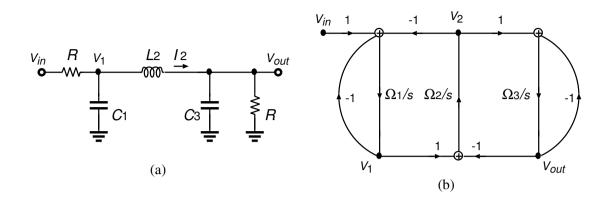

| A.1  | All-pole filter synthesis using Leap-frog simulation (3 <sup>rd</sup> -order low-pass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 11.1 | filter as an example). (a) RLC prototype ladder and (b) signal flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|      | graph (SFG) of (a).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 144  |

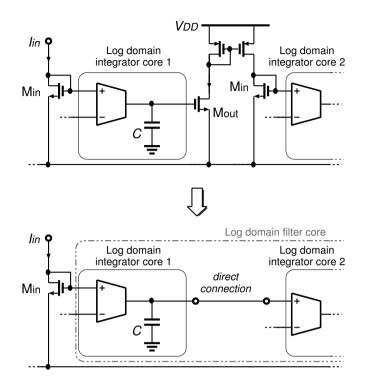

| A.2  | Principle of all-pole higher-order filters based on log domain integrators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 11.2 | [39], [46]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 145  |

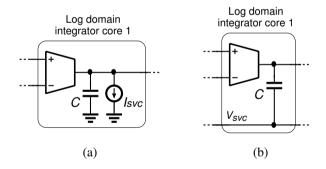

| A.3  | Log domain integrator cores in all-pole syllabic companding log domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 110  |

| 11.0 | filters using (a) current-type SVC and (b) voltage-type SVC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 145  |

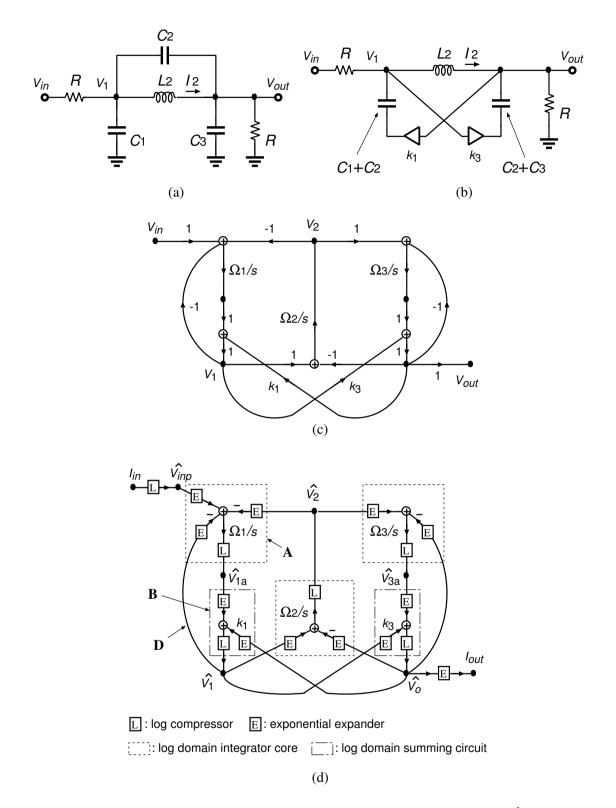

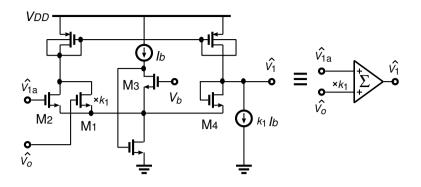

| A.4  | Log domain filter synthesis using Leap-frog simulation (3 <sup>rd</sup> -order low-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 110  |

|      | pass filter as an example). (a) RLC prototype ladder, (b) equivalent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|      | circuit of (a), (c) signal flow graph (SFG) of (a), and (d) log domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|      | SFG [71].       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 147  |

| A.5  | Log domain summing circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 148  |

| A.6  | Log domain integrator core and log domain summing circuit in syllabic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - 10 |

|      | companding filter with transmission zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 149  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | т 10 |

### Acknowledgements

I would like to express my gratitude to my supervisor Prof. Kazuyuki Wada, who has led me to a world of analog integrated circuit design and given me the opportunity of working on the interesting fields. He has encouraged and supported me to fulfill my research goal.

I am grateful to Prof. Yoshiaki Tadokoro and Prof. Takashi Ohira for reviewing my thesis and for their valuable comments and suggestions.

I would like to extend my thanks to all members of the Signal Processing Laboratory for technical and nontechnical discussions and for having fun times with me.

Finally, I dedicate this thesis to my mother Yoko whose encouragement, love, understanding and support enabled my research.

This study was partially funded by The 21st Century COE Program "Intelligent Human Sensing" and The Global COE Program "Frontiers of Intelligent Sensing" from the ministry of Education, Culture, Sports Science and Technology, and supported by VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Rohm Corporation, Toppan Printing Corporation, Cadence Design Systems, Inc., Mentor Graphics, Inc., and Synopsys, Inc. for designing and fabricating chips.

## Chapter 1

### **General Introduction**

#### 1.1 Background and Motivation

Analog circuits are required as an interface between physical quantities, such as sounds or electromagnetic waves, and a digital code described as "0" or "1," which is processed by a computer and gives us information. For a lower cost of the devices analog and digital circuits have been integrated together on a complementary metaloxide semiconductor (CMOS) chip. Furthermore, a CMOS technology scaling which means to shrink the width of the metal line and the gate length of the transistor has helped to reduce power consumption, cost, and size and to push more integration and high-speed operation in digital circuits.

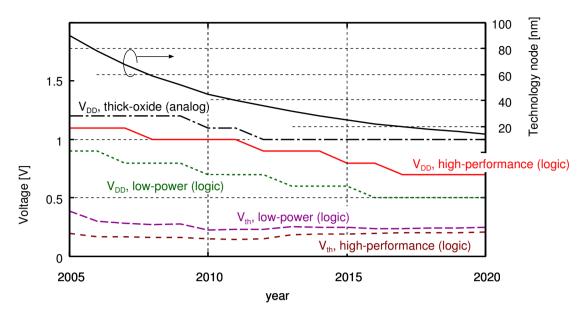

The CMOS technology scaling requires new low-supply voltage design techniques for analog integrated circuits (ICs) because of a degradation of the device breakdown voltage and a demand of low-power consumption. The International Technology Roadmap for Semiconductors (ITRS) shows the prospects of relation between technology node and power-supply voltage  $V_{DD}$  for the future as shown in Fig. 1.1 [1]. In this figure it is clearly confirmed that the shorter the width of the metal line in ICs is, the lower the supply voltage becomes. Nevertheless, a threshold voltage  $V_{th}$ of a transistor cannot be decreased like the supply voltage in digital circuits because a subthreshold leak current, which arises even as a transistor is switched off, must be suppressed. In an analog circuit design a transistor the gate-to-source voltage of which is set above  $V_{th}$  is generally used to obtain a large gain. Therefore what  $V_{th}$

Figure 1.1: Technology road map for semiconductor in the future: relation among technology node, supply voltage  $V_{DD}$ , and threshold voltage  $V_{th}$  [1].

does not reduce in comparison to  $V_{DD}$  makes it difficult to design analog circuits with a sub-micron CMOS process. There are some solutions for the above problem in analog circuit designs: using a thick oxide in a gate of a transistor [2], [3] and low- $V_{th}$ devices [4]–[6] which increase cost for additional masks. Another is to utilize several low-voltage analog circuit design techniques described in Refs. [3], [7]–[11], especially, log domain circuit design technique [12] which employs non-linearity of a transistor for linear signal processing. By use of these techniques, amplifiers [5], [13]–[15] and filters [16]–[21] under 1.0-V supply have been developed in the past several years.

In addition to the issue about lower supply voltage a dynamic range (DR) of analog circuits must be considered. Since low-supply voltage makes a signal swing in analog circuits degraded while a noise level is not decreased, its DR reduces. In general for the sake of enhancing DR an auto gain controlled (AGC) circuit is utilized in front of a filter [22]. In an AGC circuit a variable gain amplifier (VGA) the gain of which is appropriately adjusted amplifies an input signal to obtain wide DR at the output. Other techniques are described in Ref. [23]: the impedance scaling and the companding technique. The companding technique is suitable for realizing a wide DR signal processor [23], [24]. Voltage swing of internal node of a companding circuit is almost constant and a constant signal-to-noise ratio (SNR) over wide DR is brought. Especially, the dynamically adjustable biasing (DAB) technique, which is combination of the companding technique and a log domain circuit, is attractive because amplifiers on a DAB circuit are easily implemented by use of only one transistor [25], [26]. However, conventional circuits using these techniques require a power supply of 1.2 V to 3.3 V. Therefore a design technique to alleviate a trade-off between supply voltage and DR is required in any applications, for example a sub-1V filter with more than 80-dB DR which is a GSM (global system for mobile) specification.

#### 1.2 Overview of the Dissertation

This dissertation describes design techniques of low-voltage wide DR log domain filter using the DAB technique and shows measured results of prototype chips.

In Chapter 2 a conventional low-voltage operational transconductance amplifier (OTA), a filter as its application example, and several conventional techniques for wide dynamic range are reviewed. Furthermore the two classified companding techniques, instantaneous and syllabic types, are also introduced. Chapter 3 shows a synthesis method of all low-voltage instantaneous companding log domain integrators. The method clarified unknown topologies of the integrators and two instantaneous companding filters as its application example are compared through measured results. A selection of a building block is also discussed for the later Chapters in the view of higher-order filter synthesis. In Chapter 4 a low-voltage syllabic companding technique is proposed by modifying the conventional DAB technique and then an integrator and filters are designed. A control current dynamically adjusts an appropriate operating point of the circuits for low-voltage operation and wide DR. An externally linear and time invariant (ELTI) relation between an input and an output of the circuits is endured by use of new state variable correction (SVC) methods. Chapter 5 shows an optimum design method of the control current for wider DR by using DC characteristics of a low-voltage DAB-based filter and the analyzed noise expression. Since the method does not need any transient simulation, a short design time is expected. In Chapter 6 a low-voltage frequency tuning system, a voltage reference circuit, and a control circuit are described. These biasing circuits are applicable to any low-voltage log domain filters. Measured results of prototype filter chips of proposed filters are shown in Chapter 7. One of the filters is compared to the other recently published filters through a figure of merit (FOM) which is calculated from DR, bandwidth, filter order, and power consumption. Finally, Chapter 8 concludes the dissertation and the future works are given.

## Chapter 2

### **Review of Conventional Filters**

#### 2.1 Low-Voltage Filters

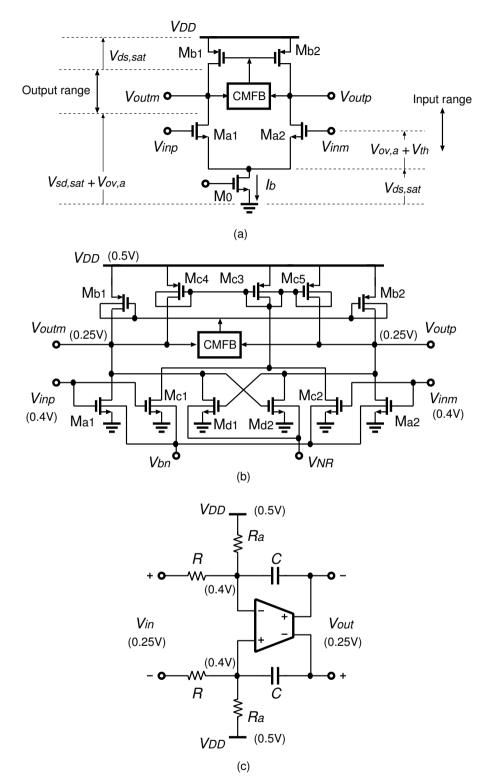

An active integrated filter is composed of passive components, such as resistors and capacitors, and operational amplifiers or operational transconductance amplifiers (OTAs) as active components by transforming an RLC prototype ladder filter into a structure using integrators [27]–[29]. These amplifiers require a power supply, and then a differential amplifier shown in Fig. 2.1 (a) is generally employed [30], [31] where a common-mode feed back (CMFB) circuit makes a common-mode output voltage  $V_{DD}/2$  and its circuitry is omitted. In this figure a required minimum supply voltage is considered. In order that a MOSFET  $M_0$  as a tail current source is biased in saturation region, its drain-to-source voltage must be larger than  $V_{ds,sat}$ . A gateto-source voltage of  $M_{a1}$  and  $M_{a2}$  requires  $V_{gs,a}$  which corresponds to the overdrive voltage  $V_{ov,a}$  plus the threshold voltage  $V_{th}$  of the MOSFETs, and thus a commonmode input voltage needs a voltage of  $V_{ds,sat} + V_{ov,a} + V_{th}$ , which equals at least 0.9 V in a standard 0.18- $\mu$ m CMOS process where  $V_{ds,sat} = 0.2$  V,  $V_{ov,a} = 0.2$  V, and  $V_{th} = 0.5$  V. In general since a common-mode input voltage is set as a half of a supply voltage  $V_{DD}$ ,  $V_{DD}$  must be larger than 1.8 V. In this case it is assumed that potentials of the output are minimum, or  $V_{ds,sat} + V_{ov,a}$ , and thus an output voltage can swing from 0.4 to 1.6 V.

Recently, an OTA with a power supply of 0.5 V and a filter as its application example have been presented in Refs. [15]–[17]. The circuitry of the OTA is shown

Figure 2.1: Operational transconductance amplifiers (OTAs) and an integrator: (a) a conventional differential amplifier as OTA, (b) a 0.5-V OTA, and (c) a 0.5-V integrator [16].

in Fig. 2.1 (b). In this figure a tail current source is removed out, while MOSFETs  $M_{ci}$  (i = 1 to 5) are added for a common-mode rejection. For enhancing DC gain of the OTA the MOSFETs  $M_{c1}$  and  $M_{c2}$  as a negative resistor are used where its value is automatically controlled by  $V_{NR}$ . The common-mode output voltage is  $V_{DD}/2 = 0.25$  V, while the common-mode input voltage is set as 0.4 V to bias the input devices,  $M_{a1}$ ,  $M_{a2}$ ,  $M_{c1}$ , and  $M_{c2}$ , in a moderate inversion region. An integrator for a filter is therefore configured as shown in Fig. 2.1 (c) where a resistor  $R_a$  is used to set a common-mode input voltage into 0.4 V. A 5<sup>th</sup>-order elliptic low-pass filter with 135-kHz cutoff has been implemented by use of the 0.5-V integrators in a 0.18- $\mu$ m CMOS with triple well process and the measured results show the filter has dynamic range of 57 dB [16].

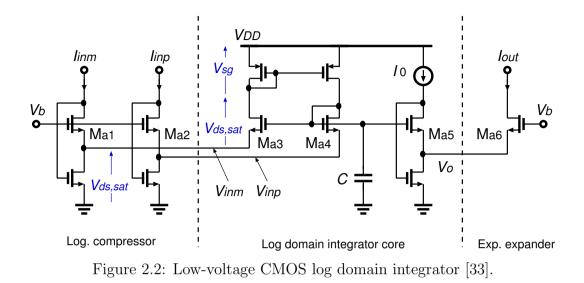

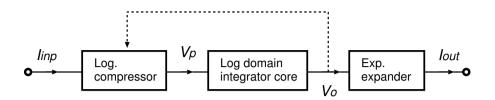

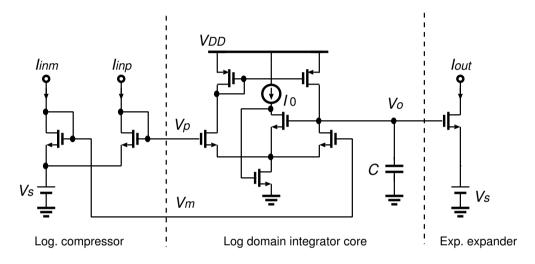

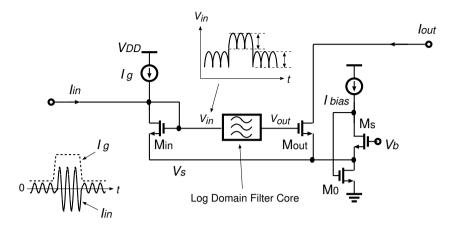

A log domain circuit is also usable for low-voltage analog filter design [12]. Log domain circuits use an exponential function of a bipolar transistor for linear signal processing [12], [32]–[36]. Since a MOSFET in weak inversion region, which means  $V_{gs} < V_{th}$ , also expresses the function, log domain circuits composed of such MOSFETs have been reported in Refs. [18], [37]–[42]. Figure 2.2 shows a CMOS log domain integrator as an example circuity [33]. A differential input current  $I_{inp} - I_{inm}$ and an output current  $I_{out}$  have a relation of linear integrator, while internal node voltages behave as a logarithmic manner for the input and the output currents. In this figure differential input currents,  $I_{inp}$  and  $I_{inm}$ , are logarithmically compressed and converted into voltages,  $V_{inp}$  and  $V_{inm}$ . The voltages are processed in log domain by a log domain integrator core, which outputs a voltage  $V_o$ . An output current  $I_{out}$  is obtained by an exponential function of a MOSFET M<sub>a6</sub>. A required supply voltage  $V_{DD}$  is equal to  $V_{sg} + 2V_{ds,sat}$ , which is about 0.6 V for a 0.18- $\mu$ m CMOS technology and 0.8 V for a 0.35- $\mu$ m one. Log domain filters are also implemented by use of floating-gate MOS (FGMOS) transistor, and then the filters can operate under 1.0-V supply [43], [44]. Measured results of these conventional log domain filters below a power supply of 1.0 V show that its dynamic ranges are around 60 dB [41]–[43]. All-pole higher-oder log domain filters are synthesized by use of log domain integrator cores as shown in Fig. 2.2 [45]–[48]. Another technique using non linearity of a MOSFET is the squire-root-domain one, which is difficult to achieve a low-voltage operation because its transistors are biased in strong inversion region,  $V_{gs} > V_{th}$  [49]–[52].

#### 2.2 Wide-Dynamic Range Techniques

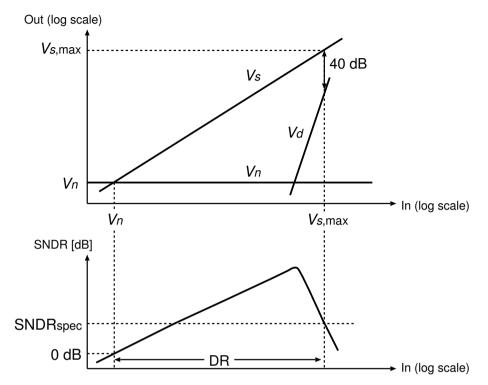

Signal-to-noise-plus-distortion ratio (SNDR) and dynamic range (DR) are important characteristics of continuous-time filters. If an input signal, an output noise, and a distortion component are denoted as  $V_s$ ,  $V_n$ , and  $V_d$ , respectively, then SNDR is expressed as

$$\text{SNDR} = 10 \log \frac{V_s^2}{V_n^2 + V_d^2} \, [\text{dB}]$$

(2.1)

where filter with a 0-dB passband gain is assumed [23], [24]. In general a noise is dominant for SNDR at a small input signal, while a distortion is so at a large input in continuous-time filters as shown in Fig. 2.3. On the other hand, DR is defined as

$$DR = 20 \log \frac{V_{s,max}}{V_n} \ [dB]$$

(2.2)

where  $V_{s,max}$  is generally an input signal under -40-dB total harmonic distortion (THD) at the output [16], [26]. If wider DR is required, one should reduce  $V_n$  or

Figure 2.3: Relation between signal-to-noise-plus-distortion ratio (SNDR) and dynamic range (DR).

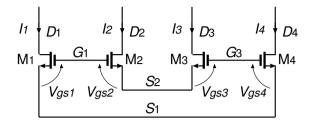

Figure 2.4: Techniques for wide-dynamic range analog signal processing: (a) a filter with an automatic gain controlled (AGC) circuit and (b) an integrator in a filter using dynamic impedance scaling technique.